This is an implementation of X-HEEP in TSMC65 LP to demonstrate X-HEEP on Silicon. It equips the Ibex core, 256kB of SRAM, a CGRA, and few peripherals.

Keywords

#systemonchip #tsmc65 #rtl2gds #microcontroller #riscv #cgra #imc #bladeTeam

Research Partners

| X-HEEP |

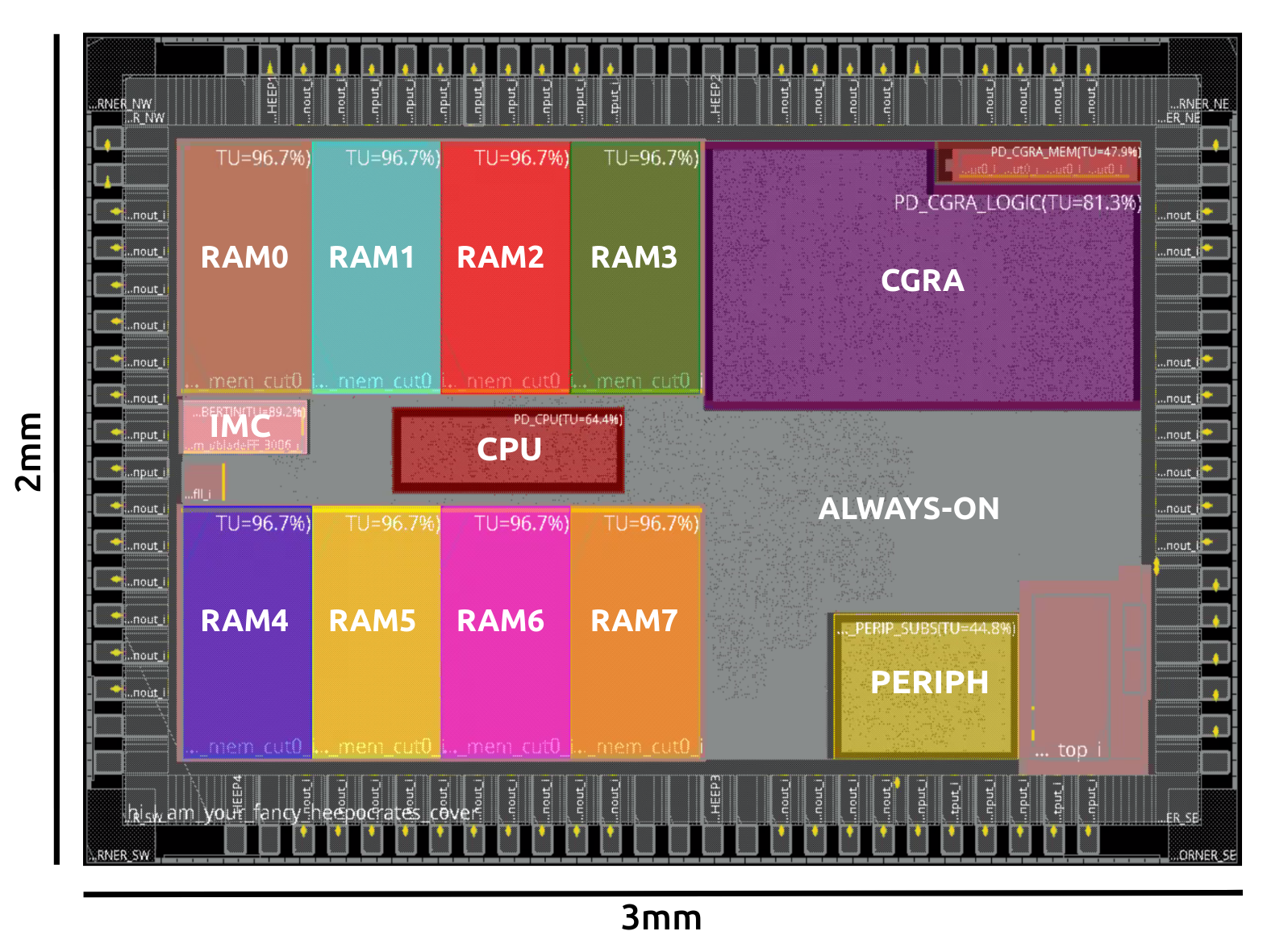

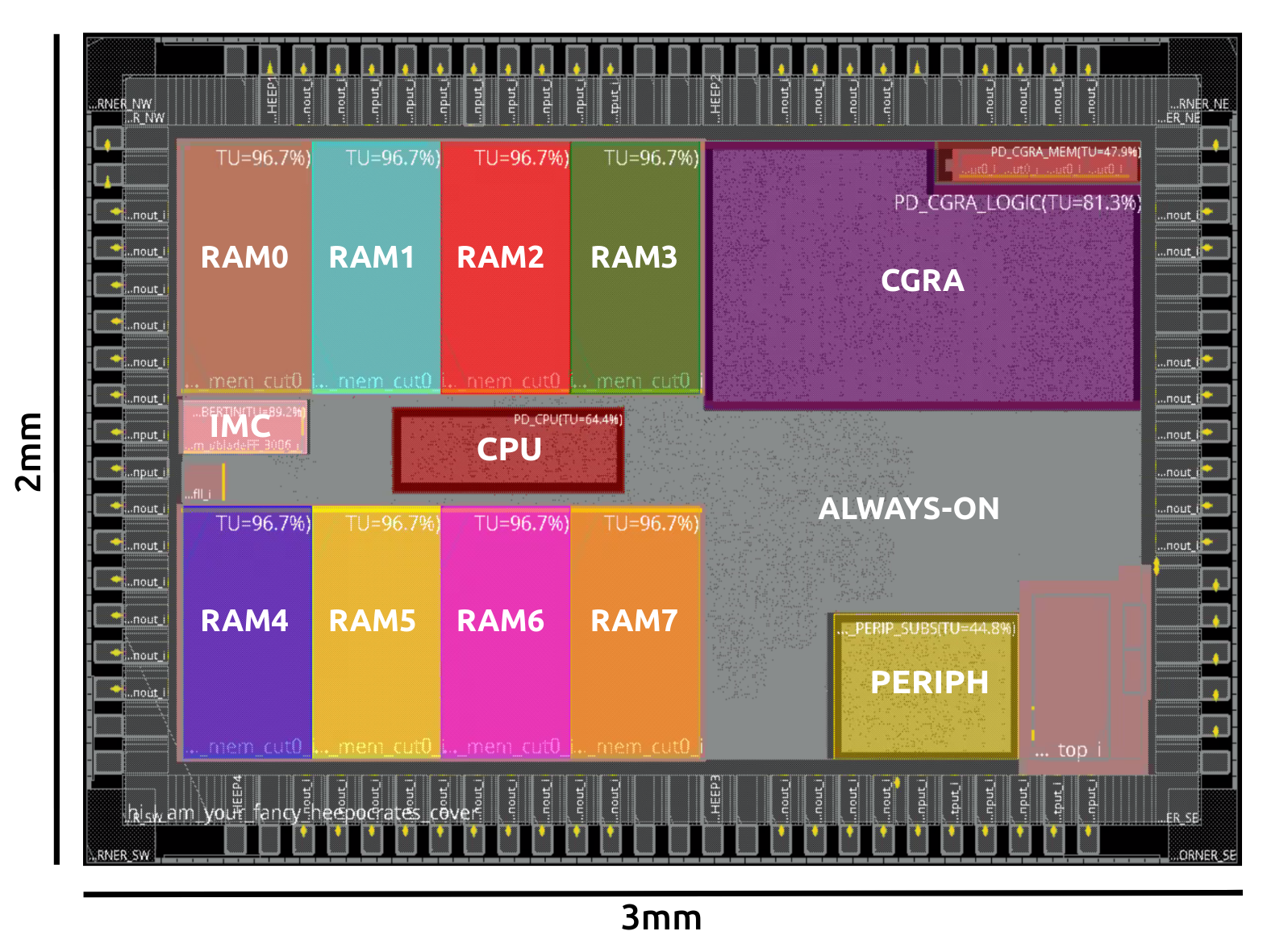

X-HEEP in TSMC65 3x2 mm2 hosting a CGRA and two instances of Blade, one called Blade for testing reasons, and one coubertin attached to the bus. Preliminary results show max frequency 250MHz and 28uW/MHz at 1.2V running a matrix multiplication. |

HEEPocrates Test Chip layout in TSMC 65nm LP

HEEPocrates Test Chip layout in TSMC 65nm LPRelated Publications

| TiC-SAT: Tightly-coupled Systolic Accelerator for Transformers |

| Amirshahi, Alireza; Klein, Joshua Alexander Harrison; Ansaloni, Giovanni; Atienza Alonso, David |

| 2023-01-16 | Conference Paper | |  |  |

| Using Algorithmic Transformations and Sensitivity Analysis to Unleash Approximations in CNNs at the Edge |

| Ponzina, Flavio; Ansaloni, Giovanni; Peon Quiros, Miguel; Atienza Alonso, David |

| 2022-07-19 | MDPI Micromachines - Special Issue "Hardware-Friendly Machine Learning and Its Applications" | |  |  |  |  |

| Machine-Learning Based Monitoring of Cognitive Workload in Rescue Missions with Drones |

| Dell'Agnola, Fabio; Jao, Ping-Keng; Arza, Adriana; Chavarriaga, Ricardo; R. Millan, Jose del; Floreano, Dario; Atienza, David |

| 2022-06-29 | IEEE Journal of Biomedical and Health Informatics | |

| A hardware/software co-design vision for deep learning at the edge |

| Ponzina, Flavio; Machetti, Simone; Rios, Marco Antonio; Denkinger, Benoît Walter; Levisse, Alexandre Sébastien Julien; Ansaloni, Giovanni; Peon Quiros, Miguel; Atienza Alonso, David |

| 2022 | IEEE Micro - Special Issue on Artificial Intelligence at the Edge | |  |  |  |

| E2CNN: Ensembles of Convolutional Neural Networks to Improve Robustness Against Memory Errors in Edge-Computing Devices |

| Ponzina, Flavio; Peon Quiros, Miguel; Burg, Andreas Peter; Atienza Alonso, David |

| 2021 | IEEE - Transactions on Computers | |  |  |  |