Your mission:

ADC research in the current decade has largely been stagnant as ADC architectures on all fronts are simply converging to a capacitor-array-based SAR ADC. Of course, there is a lot of work to do in this direction, but we, at MSIC Lab, are envisioning something grander and different: we will focus on the density of ADCs.

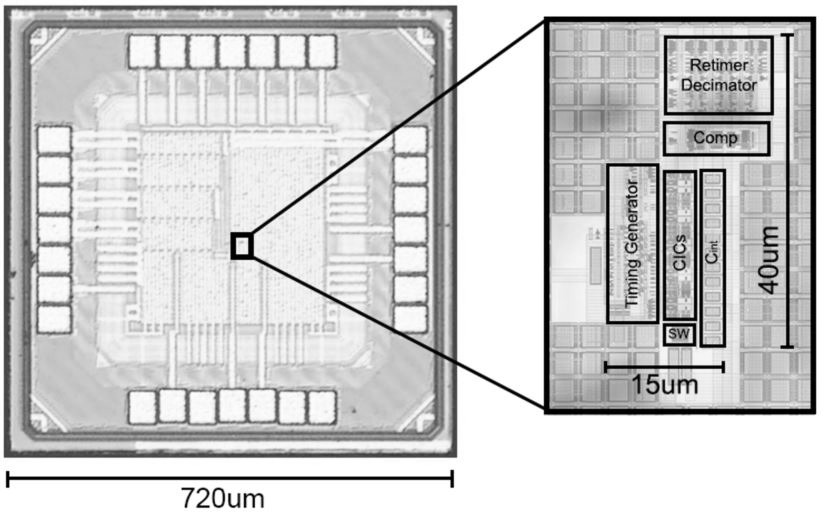

Smaller ADCs are welcome everywhere; in in-memory computing, high-speed wireline communication, 5G/6G wireless, and sensor readout, to just name a few. We are leading a novel architectural study of ADCs in these domains aiming to achieve the highest density as well as energy efficiency. The new architectures will be based on combining conventional techniques and our ciDAC technology. The mission for the new Ph.D. student is to lead such investigations in multiple ADC design directions: interleaved ADC, parallel ADC, and oversampling ADC.

We have multiple positions for this task and are looking for talented mixed-signal circuit designers ready to pump some energy into invigorating architectural research in the domain of ADCs.

Main duties and responsibilities include :

Develop novel ciDAC-based ADC architectures and perform model-based trade-off analysis

- Propose and implement novel ciDAC-based ADC architectures

- Understand and explore the fundamental trade-offs in noise, mismatch, energy, ENOB, speed, etc.

- Understand and explore the drive from the application space

Your profile:

- Solid background and/or experience in ADC design

- Knowledge of ADC characterization

- Excellent track record on the following topics:

- electronic devices

- circuit theory

- noise theory

- signal processing

- analog circuits design

- integrated circuits design flow:

analog design, digital synthesis, layout, place and route…

- Necessary skills:

- Fluency in using Cadence Virtuoso Suite

- Fluency in using SPICE simulators (HSPICE, FineSim, AFS, etc.)

- Preferred skills

- Fluency in scripting with Python

- Fluency in running simulations on the Linux terminal

- Fluency in using PCB design suite (Altium)

We offer :

- A multidisciplinary environment

- Excellent working conditions

- Laboratory based in Neuchâtel campus (the building is quite new!)

Preferred start date :

January 1, 2023 +/- 2 months

January 1, 2023 +/- 2 months

Duration :

4 years

4 years

Contact :

Candidates must send their application to Prof. Kyojin Choo

Candidates must send their application to Prof. Kyojin Choo