Availability: Spring-Fall 2023

Contact: Rassul Bairamkulov ([email protected])

Background:

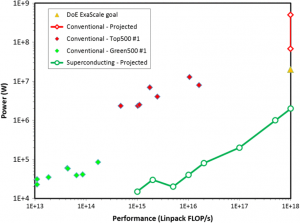

Superconductive electronics (SCE) is a promising candidate for supplementing or replacing existing CMOS VLSI systems. Rapid Single-Flux Quantum (RSFQ) is one of the most advanced superconductive technologies operating at tens of gigahertz while reducing the operating power by up to three orders of magnitude as compared to conventional semiconductor systems, even considering the cryogenic cooling power [1] (see Fig. 1).

RSFQ systems can benefit many industries, such as cloud computing, space electronics, and quantum computing. Achieving VLSI complexity in RSFQ remains an elusive task due to fundamental differences between conventional and superconductive technologies.

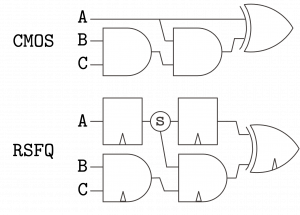

Gate-level pipelining is arguably the most important feature of superconductive circuits. Most logic gates, such as NOT and XOR are clocked, necessitating path balancing. This limitation requires the inputs to each gate to have equal logic level, as shown in Fig. 2. The overhead of path balancing can be prohibitively large, often increasing the size of the circuit by 400%.

To tackle this issue, a novel gate compounding technique is proposed, realizing more complex functionality in fewer clock cycles. This technique however requires updating the RSFQ standard cell library which, in turn, requires electrical verification of the novel RSFQ standard cells.

Project tasks:

- To aid the development of the new cell library, the novel RSFQ cells need to be implemented at circuit level using specialized SPICE-like tools (e.g. WRSPICE, Virtuoso, JoSIM).

- Using simulation tools, the characteristics of each cell need to be evaluated

- Using specialized (e.g. JoSIM tools) or custom (e.g. based on SciPy) optimization tools the operating margins of the novel cells need to be maximized to improve the manufacturing yield

- Conversion tool between the logic level (e.g. Verilog) and circuit level (SPICE) description is needed to verify the functionality of complex RSFQ systems.

Requirements:

- Basic knowledge of

- circuit simulation tools (e.g. Cadence Virtuoso or any version of SPICE)

- C++ or Python for basic scripting

- high-level circuit description formats, such as Verilog or VHDL

- High-level understanding of optimization process and tools

Learning outcomes:

- Introduction to

- superconductive electronics

- standard cell design

- logic synthesis

- Experience in

- circuit analysis

- optimization tools

- command line interface

Related literature:

Overview of superconductive electronics from the perspective of large scale computing:

[1] Holmes, D. S., Ripple, A. L., & Manheimer, M. A. (2013). Energy-efficient superconducting computing— Power budgets and requirements. IEEE Transactions on Applied Superconductivity, 23(3), 1701610-1701610.

A relatively recent path balancing algorithm for the original RSFQ logic library. Also provides some background on path balancing problem.

[2] Pasandi, G., & Pedram, M. (2018). PBMap: A path balancing technology mapping algorithm for single flux quantum logic circuits. IEEE Transactions on Applied Superconductivity, 29(4), 1-14.

A recent book providing good background for SFQ circuit design

[3] Krylov, G., & Friedman, E. G. (2022). Single Flux Quantum Integrated Circuit Design. Berlin: Springer.

For more information, please contact Rassul Bairamkulov [email protected]