#### Invitation to the WEEE - Workshop on Energy Efficient Electronics and Applications

We are pleased to invite you to participate in the 2nd *Workshop on Energy Efficient Electronics and Applications (WEEE)* to take place at EPFL in Lausanne, Switzerland on January 9-11, 2014. This workshop is the perfect place to acquire knowledge, discuss with colleagues, expand your professional network, and initiate research collaborations.

The first two days of the workshop (January 9-10) focus on Keynotes and short lectures by high-profile invited speakers from academia and industry as well as contributed posters from researchers and PhD students during the coffee breaks.

For the optional third day (January 11) we will move to mountain/skiing resort of Leysin to continue in a quiet and relaxed atmosphere with a mix of research and student presentations, discussions, and leisure activities to foster collaborations and exchange among research groups. (Hotel options for extension to Sunday are also provided.)

We encourage you to submit short (50-100 words) abstracts for poster sessions during the coffee breaks of the first two days of the workshop and for presentations of PhD students on the third day. The best PhD presentation will receive an award sponsored by the IEEE-CAS Society, Switzerland.

## Details about the workshop, are available online at <a href="http://tcl.epfl.ch/WEEE">http://tcl.epfl.ch/WEEE</a>.

#### About the workshop:

The objective of this workshop is to bring together experts, from both industry and academia, in system architecture, circuit design, and technology to discuss the challenges and the latest trends in the development of low-power and ultra-low-power embedded systems. The workshop covers

- Low-power embedded systems and computing architectures

- Ultra-low power and sub-threshold circuit design

- Variability and reliability issues in modern process technologies and corresponding new design paradigms

- Advanced CMOS and More-than-Moore Technologies

for mobile, wearable, and embedded applications.

The workshop will feature a number of Keynote presentations, followed by extensive Q&A sessions for interactive discussions. Furthermore, we will have a number of invited technical presentations from experts in the field. PhD students will have the opportunity to present their research in a PhD forum to be held during an optional third day in the beautiful mountain resort of Leysin. We expect a mixed audience from industry and academia to thereby strengthen the link between companies and research institutions.

Registration options will include participation in all workshop activities, lodging (1-4 nights), transportation, and a gala dinner.

For more information, visit <a href="http://tcl.epfl.ch/WEEE">http://tcl.epfl.ch/WEEE</a> or contact us by email.

Thank you,

Prof. Andreas Burg, EPFL andreas.burg@epfl.ch

Prof. Alexander Fish, BIU alexander.fish@biu.ac.il

Dr. Vasilis Pavlidis, Manchester pavlidis@cs.man.ac.uk

| Thursday, January 9th 2014, Room : BC 420 |                                                                                                                                                 |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 09:00 - 09:15                             | Workshop Opening and Welcome Andreas Burg, EPFL                                                                                                 |  |  |  |

| 09:15 – 10:15                             | "Power Efficient Heterogeneous Integrated Systems" <b>Prof. Eby Friedman</b> , <i>University of Rochester</i>                                   |  |  |  |

| 10:15 – 10:45                             | "Computing with Leakage Currents"  Prof. Yusuf Leblebici, EPFL                                                                                  |  |  |  |

| 10:45 - 11:15                             | COFFEE BREAK and POSTER SESSION                                                                                                                 |  |  |  |

| 11:15 – 12:15                             | "Handling Uncertainty and Approximation in Variability Affected Computing"  Prof. Rajesh Gupta, University of California San Diego              |  |  |  |

| 12:15 - 13:45                             | LUNCH                                                                                                                                           |  |  |  |

| 13:45 – 14:45                             | "Computing in the Nanoscale Era – A Shannon-inspired Perspective" <b>Prof. Naresh Shanbhag</b> , <i>University of Illinois Urbana-Champaign</i> |  |  |  |

| 14:45 – 15:15                             | "Ultra Low-Power Radios (including MEMS-based Radio)" <b>Prof. Christian Enz</b> , <i>EPFL</i>                                                  |  |  |  |

| 15:15 - 15:45                             | COFFEE BREAK                                                                                                                                    |  |  |  |

| 15:45 – 16:30                             | "Bringing Low Power Sensing to the Marketplace - Technologies and Applications" <b>Dr. Matthias Streif</b> , SENSIRION                          |  |  |  |

| 16:30 – 17:15                             | "Energy-efficient temperature sensors" <b>Prof. Kofi Makinwa,</b> <i>TU Delft</i>                                                               |  |  |  |

# 19:00 – 22:30 Gala Dinner at the Restaurant Le Debarcadère in St-Sulpice

| Friday, January 10th 2014, Room : BC 420 |                                                                                                                           |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| 09:00 – 10:00                            | "Energy-Efficient, Resilient Circuit Design in High-Performance Technologies" <b>Dr. Jim Tschanz</b> , <i>INTEL</i>       |  |  |

| 10:00 – 10:30                            | "Ultra-Low Power Systems-on-Chips and some Applications" <b>Prof. Christian Piguet</b> , CSEM                             |  |  |

| 10:30 - 11:00                            | COFFEE BREAK and POSTER SESSION                                                                                           |  |  |

| 11:00 – 12:00                            | "UTBB FD-SOI technology for Extreme Power Efficient SOCs"  Philippe Flateresse, ST Microelectronics                       |  |  |

| 12:00 - 13:30                            | LUNCH                                                                                                                     |  |  |

| 13:30 – 14:30                            | "Managing variability in Near-threshold clustered multiprocessors" <b>Prof. Luca Benini</b> , <i>ETH Zurich</i>           |  |  |

| 14:30 – 15:00                            | "Exploiting Biosignals Features for Ultra-Low Power Personal Monitoring Systems" <b>Prof. David Atienza</b> , <i>EPFL</i> |  |  |

| 15:00 - 15:30                            | COFFEE BREAK                                                                                                              |  |  |

| 15:30 – 16:15                            | "Digilog: Biosignal Sensing" <b>Prof. Dejan Markovic</b> , <i>UCLA</i>                                                    |  |  |

| 16:15 – 16:45                            | "Alternative Embedded Near-VT SRAMs"  Prof. Joachim Rodrigues, LUND University                                            |  |  |

| 16:45 – 17:15                            | Plenary Session: The Future of Low Power Design                                                                           |  |  |

| 18:00 | Bus pickup for transfer to Leysin (with reservation)        |  |

|-------|-------------------------------------------------------------|--|

| 20:00 | Leysin Welcome Dinner Apero (sponsored by IEEE Switzerland) |  |

| Saturday, January 11th 2014, Mercure Classic Hotel Leysin |                                                                                           |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| 08:30 - 08:55                                             | "Low power trade-off in Fault Tolerant ASICs"                                             |  |  |

|                                                           | Dr. Milos Kristic, IHP                                                                    |  |  |

| 08:55 - 10:20                                             | PhD Forum Part 1: Short presentations (3 min. each)                                       |  |  |

| 10:20 - 10:50                                             | COFFEE BREAK                                                                              |  |  |

| 10:50 - 11:30                                             | PhD Forum Part 2: Posters                                                                 |  |  |

| 11:30 – 11:55                                             | "Adaptive hardware and voltage conversion, novel possibilities in energy savings"         |  |  |

|                                                           | Dr. Lauri Koskinen, Aalto Univ.                                                           |  |  |

| 11:55 – 12:20                                             | "Design and Exploration of Inexact Floating-Point Architectures for Atmospheric Modeling" |  |  |

|                                                           | Dr. Jaume Joven Murillo, <i>EPFL</i>                                                      |  |  |

| 12:20 - 13:30                                             | LUNCH                                                                                     |  |  |

| Activities: Hiking, Skiing, Enjoy the view, Snow Tobbogan |                                                                                           |  |  |

|                                                           |                                                                                           |  |  |

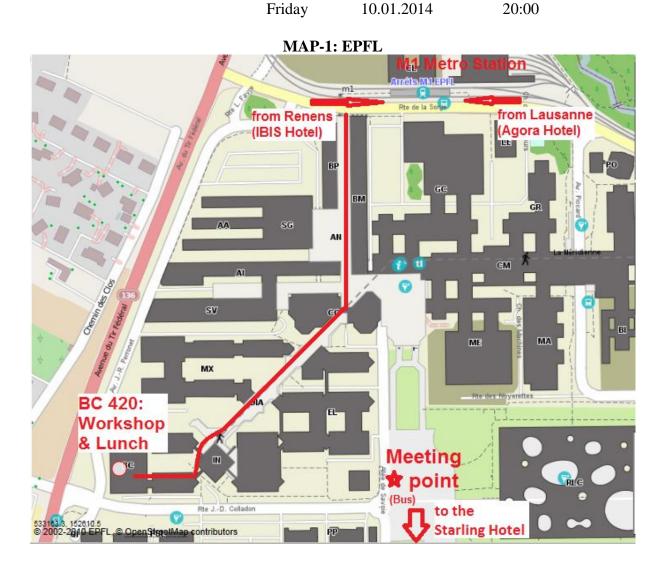

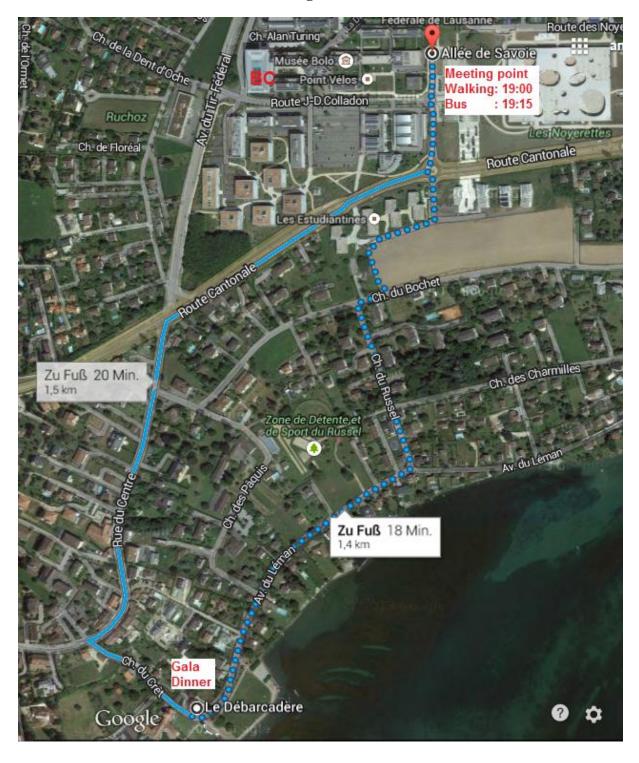

Workshop Location EPFL, BC 420 (4th floor of the BC building) Directions from Metro Station: see map-1 Arrival / Registration EPFL, BC 420 Thursday 09.01.2014 08:15 - 09:00 Friday 10.01.2014 08:15 - 09:00 Gala Dinner Restaurant « Le Debarcadère » in St.-Sulpice Thursday 09.01.2014 19:00 (Apero) 19:45 (Dinner) How to get there? o Bus pickup from IBIS Hotel 18:45 o Bus pickup from EPFL Meeting Point (see map-1) 19:15 o Walking: 10-15 min from EPFL (see map-2) starting from EPFL Meeting Point at 19:00 Bus transfer to Leysin **EPFL** Meeting Point Friday 10.01.2014 18:00 IEEE Dinner Apero in Leysin

Mercure Hotel Leysin

**MAP-2:** Walking to the Gala Dinner

# PhD Forum Posters

### Presentation information:

- The PhD forum will take place Saturday 11.01.2014 in Leysin comprising

- o Preview session: a short 3 minutes pitch with 3-4 slides maximum (Part-1)

- o Poster: A poster (A0) that will be on display in the poster session following the preview session (Part-2)

- *Optional*: posters can also be shown during the Friday Coffee Breaks of the main workshop at EPFL (for time slot see the program below)

|               | 2014, MORNING o       |                    |                                                                                                                                                          |

|---------------|-----------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| David         | Bellasi               | ETHZ-IIS           | Low-Power Design Challenges of a Multi-Channel<br>Biomedical Monitoring SoC                                                                              |

| Amiri Omid    | Talebi                | EPFL               | Design Methodology and Integration of a 1.8GHz Outphasing Power Amplifier for Mobile Terminals                                                           |

| Michael       | Gautschi              | ETHZ-IIS           | A Customized, High-IPC OpenRISC Processor in an Ultra-<br>Low Power Cluster with a Shared L1 Memory                                                      |

| Pirmin        | Vogel                 | ETHZ-IIS           | Efficient Parallel Beamforming for 3D Ultrasound Imaging                                                                                                 |

| Michael       | Schaffner             | ETHZ-IIS           | An Adaptive Approximate Computing Technique for<br>Reducing the Complexity of a Direct-Solver for Sparse<br>Linear Systems in Real-Time Video Processing |

| Francesco     | Conti                 | UNIBO              | Architectural heterogeneity: bringing many-cores in the dark silicon era                                                                                 |

| Francesco     | Paci                  | UNIBO              | Energy-aware People Counting in real-world WSN                                                                                                           |

| Guerric       | de Streel             | UCLOUVAIN          | Study of Back Biasing Schemes for ULV Logic from Gate Level to IP Level                                                                                  |

| Francesco     | Fraternali            | UNIBO              | Monitoring and Resource Management Techniques for<br>Energy Efficiency in Supercomputer Environment                                                      |

| Jeremy        | Constantin            | EPFL               | Application-Specific Processor Design for Low-<br>Complexity & Low-Power Embedded Systems                                                                |

| Friday 10.01. | 2014, <b>AFTERNOO</b> | N coffee break &   | & Saturday 11.01.2014                                                                                                                                    |

| Filippo       | Casamassima           | UNIBO              | Activity aware power management for motion sensing body area network nodes                                                                               |

| Viacheslav    | Yuzhaninov            | Bar Ilan           | Full-Swing Gate Diffusion Input logic: Case-study of low-<br>power CLA adder design                                                                      |

| Andreou M.    | Charalambos           | Univ. of<br>Cyprus | Low-Power, Low-Area, Wide-Temperature-Range Voltage<br>Reference for Energy Harvesting Systems                                                           |

| Itamar        | Levi                  | Bar Ilan           | Dual Mode Logic (DML) – Overview, concepts and use                                                                                                       |

| Babak         | Mohammadi             | Lund Univ.         | A 6.25um2 single stage 28fJ per cycle, 120mV to 1.2V<br>Level Shifter                                                                                    |

| Nikola        | Katic                 | EPFL               | A 5.43-uW 0.8-V Sub-threshold Current-Sensing Sigma-<br>Delta ADC for Low-Power Sensor Interfaces                                                        |

| Matthew       | Turnquist             | Aalto Univ.        | DC-DC converter design constraints for adaptable microprocessors that target the minimum-energy point (MEP)                                              |

| Yasser        | Sherazi               | Lund Univ.         | Design Exploration of a 65 nm Sub-VT CMOS Digital Baseband                                                                                               |

| Ubaid         | ur Rehman<br>Ahmad    | IMEC               | A C-Programmable Reconfigurable ASIP for near-Optimal MIMO Detection Performance                                                                         |

| Pascal        | Meinerzhagen          | EPFL               | Embedded Memories: from Sub-VT to Error Resilient Systems                                                                                                |

### **Hotel Information**

## Lausanne / EPFL Workshop

#### Starling Hotel:

- http://www.shlausanne.com/

- Located right at EPFL across the street from the ROLEX Center (see MAP-1)

- From Lausanne to Hotel: take Metro M1 toward Renens till stop EPFL

- From Morges train station to Hotel: Taxi (~30.- CHF) or Bus 701 toward Bourdonette until *Parc scientifique*

- From Renens train station to Hotel: Metro M1 toward Lausanne-Flon till stop EPFL

- To conference venue at EPFL: walking distance (5 minutes) see Map-1

- Address: Route Cantonale 31, 1025 Saint-Sulpice, Suisse; Tel.: +41 21 694 85 85

### Agora Swiss Night Hotel:

- <a href="http://www.fassbindhotels.com/agora\_hotel.html">http://www.fassbindhotels.com/agora\_hotel.html</a>

- Located in the center of Lausanne

- From Lausanne railway station to Hotel: walk 5-10 minutes downhill (see map)

- To conference venue (2 options):

- 1. Walk uphill toward railway station, take a train to Renens, from Renens take M1 Metro toward Lausanne-Flon and get off at stop *EPFL*

- 2. Taxi: get a Taxi at the railway station until EPFL (cost: around 35.- CHF)

- <a href="http://www.ibis.com/fr/hotel-7599-ibis-budget-lausanne-bussigny-ex-etap-hotel/index.shtml">http://www.ibis.com/fr/hotel-7599-ibis-budget-lausanne-bussigny-ex-etap-hotel/index.shtml</a>

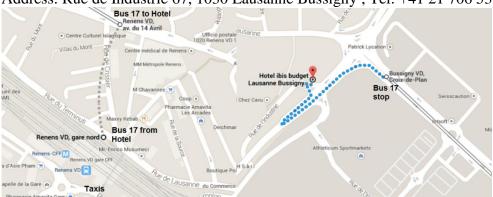

- Located at Bussigny, west of Lausanne

- Arriving by train: take train to Renens, from Renens

- o Take a Taxi to the Hotel (25.- CHF)

- O Walk north to *avenue 14 Avril* (see map below) and Take Bus #17 toward Crissier, get off at stop *Croix-de-Plan* and walk to Hotel (see map below)

- To conference venue: walk to Bus #17 stop *Croix-de-Plan* (see map below) and take Bus toward Renens and get off at stop *Renens gare nord*, from Renens train station take Metro M1 toward Lausanne-Flon and get off at stop *EPFL*; or Taxi ~30.- CHF

Address: Rue de Industrie 67, 1030 Lausanne Bussigny; Tel: +41 21 706 53 53

# Leysin Retreat / PhD Forum

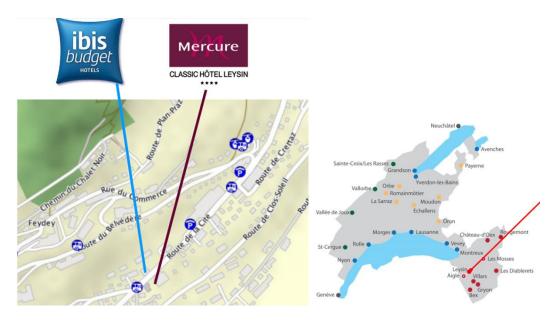

### Mercure Classic Hotel Leysin:

- Conference Venue

- http://www.mercure.com/de/hotel-6848-mercure-classic-hotel-leysin/index.shtml

- Address: Route de la cite, 1854 Leysin, Suisse; Tel: +41 24 493 06 06

## IBIS Budget Hotel Leysin:

- http://www.ibis.com/de/hotel-8567-ibis-budget-leysin/index.shtml

- Located across the street from the Mercure Classic Hotel (Conference Venue)

- Address: Route de la Cite, CP 221, 1854 Leysin, Suisse; Tel: +41 24 493 06 66

# Other useful information

Swiss Train Timetable: <a href="http://www.sbb.ch">http://www.sbb.ch</a>

Emergency Mobile Phone: +41-79-402 64 34 (Andreas Burg)

WiFi access at EPFL:

1. Network: EDUROAM

2. Network: *EPFL* Login: x-weee Password: valmed57