## Design of a Submodule of a Modular Multilevel Converter

|                                 |                                                    |          |                                                                |

|---------------------------------|----------------------------------------------------|----------|----------------------------------------------------------------|

| Professor:                      | Prof. Drazen Dujic                                 | ELH-111  | <a href="mailto:drazen.dujic@epfl.ch">drazen.dujic@epfl.ch</a> |

| Scientific Assistant Contacts:  | n/a                                                |          |                                                                |

| Project Type:                   | MSc Thesis                                         | Section: | SEL                                                            |

| Official Start Date:            | 16.02.2026                                         |          |                                                                |

| Submission of Final Report:     | 19.06.2026                                         |          |                                                                |

| Presentations at Group Meeting: | Mid-term and Final Presentations (dates TBD)       |          |                                                                |

| Delivery of project results:    | Schematic, Simulation Files, Prototype, MSc Thesis |          |                                                                |

### Context, Background, and Motivation:

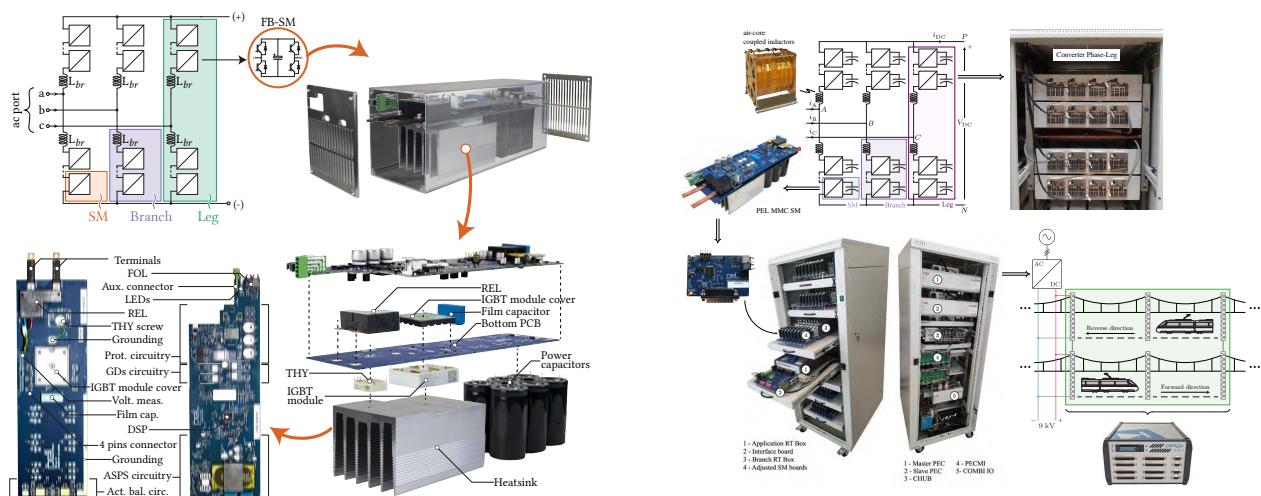

The Power Electronics Laboratory is currently developing a Matrix Modular Multilevel Converter (M3C), with 6kVac input and output 3-phase voltages, and ratings of 600kW. The M3C has nine branches, and each branch will be implemented as a string of eight full-bridge submodules (SMs) to reuse an existing control system. This implies that each SM will be operated with DC link voltages up to 2kV, needing 3.3kV rated power semiconductors for its realization. Power ratings of each SM are approximately 8.5kW (600kW / 72 SM). There is significant preliminary conceptual work that has already been done, but many design improvements and optimizations are still needed.

### Project Objectives:

Project objectives are to develop and validate a prototype of the M3C submodule. Fig. 1 illustrates details of the available design realized with 1.2kV IGBTs, hence termed low voltage (LV) submodule. The new medium voltage (MV) submodule will preserve many conceptual solutions, but it requires significant hardware changes, due to higher operating voltage and use of 3.3kV power semiconductors. Complete local control system will be preserved (TI C2000 DSP), with minimalistic changes, due to already available and tested control algorithms, using available Rt-HIL systems at the Power Electronics laboratory. The main part of the MSc thesis work is:

- Power hardware design of a full-bridge MV submodule

- Electrical sizing and selection of relevant elements

- Altium schematic and PCB design

- Mechanical design of the enclosure considering forced air cooling

- Prototyping and testing

Figure 1. Left: Details of the existing LV submodule power design. Right: Illustration of the RT-HIL setup.

**Prerequisite knowledge:**

- Power electronics converters

- Electric circuit design

- Altium

**Available equipment:**

- All the equipment required to fulfill the project's goals is available

- Preliminary design of the MV submodule is available as a starting point

**Methodology and foreseen steps of the project:**

- Getting familiar with M3C operating principles

- Getting familiar with the existing LV and MV submodules designs

- Design calculation and validation through simulations

- Electrical and mechanical design

- Prototyping and laboratory testing

**Student gain:**

- High-power converter design

- Modular multilevel converter design

- Protection of power electronic conversion systems

- High voltage design

- Power electronics integration

**References:**

- Will be provided as needed