## **MOSFET Compact Model Extensions for Circuit** Simulation: A Perspective from Industry

## **Workshop on Next Generation MOSFET Compact Model**

EPFL, December 15-16, 2011 Presenter: André Juge

TRD / STD / T2D

# Abstract

- MOSFET Compact Model Extensions for Circuit Simulation: A Perspective from Industry

- While CMOS Technology scaling has been steadily pursued to offer deca-nanometer devices, Circuit Design Community has benefited from successful development of core compact models able to capture important aspects of MOSFET electrical behavior in Circuit simulation tools. While BSIM4 models is still widely used within Industry for planar Bulk and SOI CMOS technologies, new MOSFET model generation (PSP, HiSIM...) has enabled high accuracy for design of Analog-Rf Circuits. Last, innovative modeling solutions are coming to Industry for new devices like planar FDSOI or 3D Finfet transistors.

- Beyond the successful development of core device models from Academia, model extensions need to be developed in Industry for a bunch of Technology and Design dependent effects, in close interaction with the Design tool providers to enable adaptation of Design flow.

- Presentation will overview and highlight examples of modeling extensions developed in Industry to account for realistic conditions in device operation, considering device design and circuit operation; examples of applications dealing with modeling of MOSFET Parasitics, Layout Proximity effects, Process variations, and Simulation of Degradation will be presented. The presentation is intended to bring compact modelers with a survey of such effects through their potential impact, and examples of implementation.

- MOSFET Compact Model Extensions for Circuit Simulation: A Perspective from Industry

- Objective

- Parasitic capacitances

- Layout Proximity effects

- Process variations and Statistical Variability

- Reliability aware Design

- Summary and Perspective

## Objective

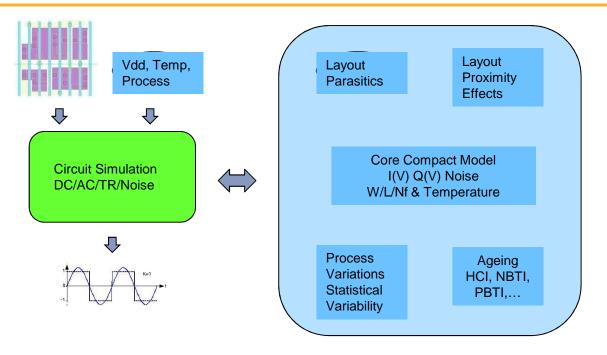

□*Core* models primarily account for Bias, Geometry (W/L/NF) and Temperature dependences of devices characteristics, and need information from other tools to account for real Design, Manufacturing, and Operating conditions.

□ Extended models are developed in Industry to account for MOSFET Parasitics, Layout Proximity effects, Process Variations, Statistical Variability, met by individual components after circuit integration, and Ageing effects considering device operation conditions.

*Circuit simulation methodologies* need to be developped concurrently with modeling effort to allow manufacturing of high yield and reliable products. Integration of Solutions in Design flow is a must.

- Extrinsic Parasitic capacitances

- Dependences to Layout

- Modeling/Simulation approach

- Perspective and ITRS

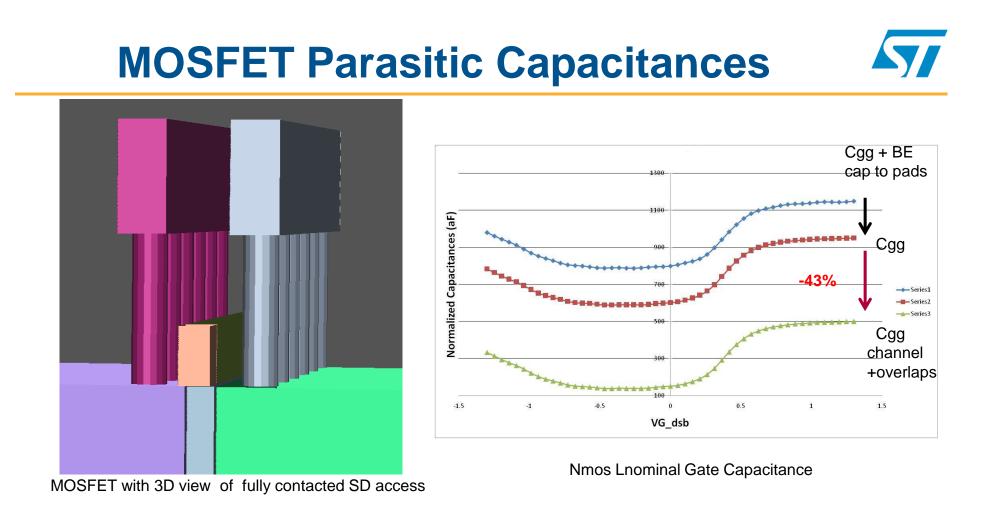

- Even for Planar Mosfets, Parasitic Capacitances surrounding gate is a 3D problem

- Cgg @Lnom almost x2 through lateral coupling between Gate and SD regions

- Cgg depends on W/L, S/D cts number/pitch, distance between gate and S/D cts

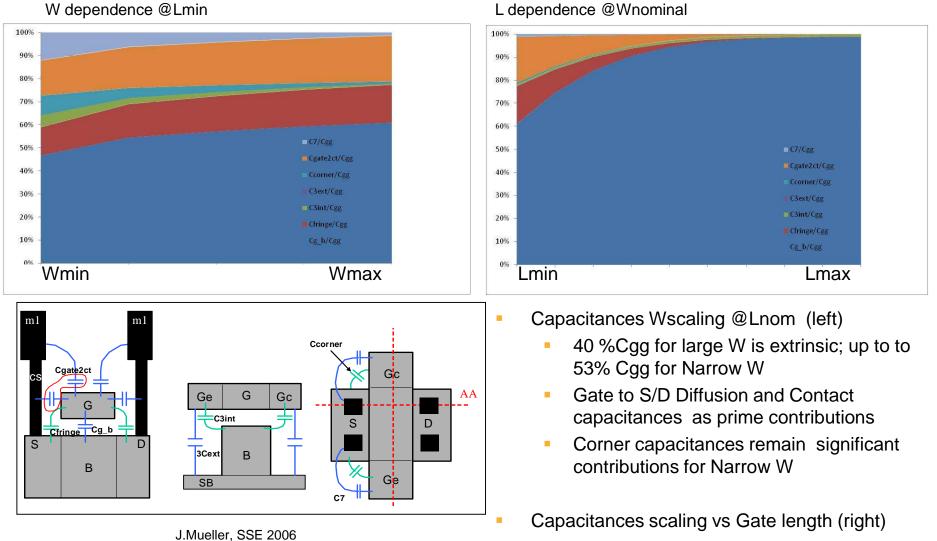

### Scaling of MOSFET Capacitance partitioning on gate W/L

L dependence @Wnominal

### **STMicroelectronics**

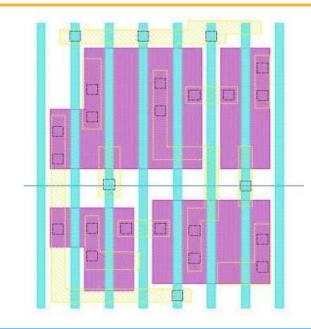

## MOSFET capacitances in real Design (S/D Contact Position vs Gate)

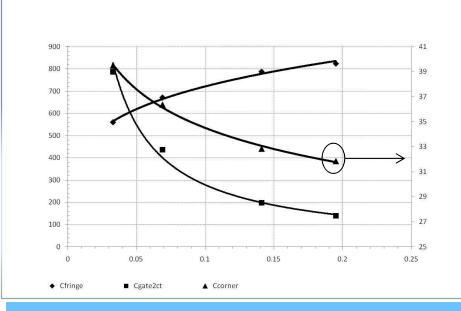

Scaling Capacitances vs distance S/D Cts to Gate

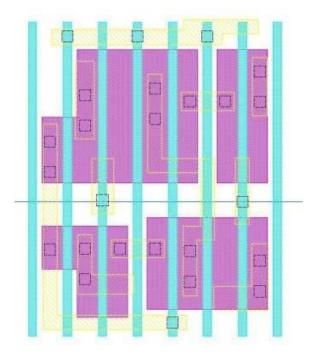

Semi-regular Std cell layout (Example)

- Capacitance dependence on SD contact position and number of contacts is significant and must be accounted in real designs

- Solutions:

- Core models or PEX tools, provided number of Mosfet instance parameters is kept minimum for large size circuit simulation

- Pre-Layout design phase: compact core model, with limited layout assumptions

- Post-Layout design phase: PEX tool more adaptative to deal with variations in Layout style.

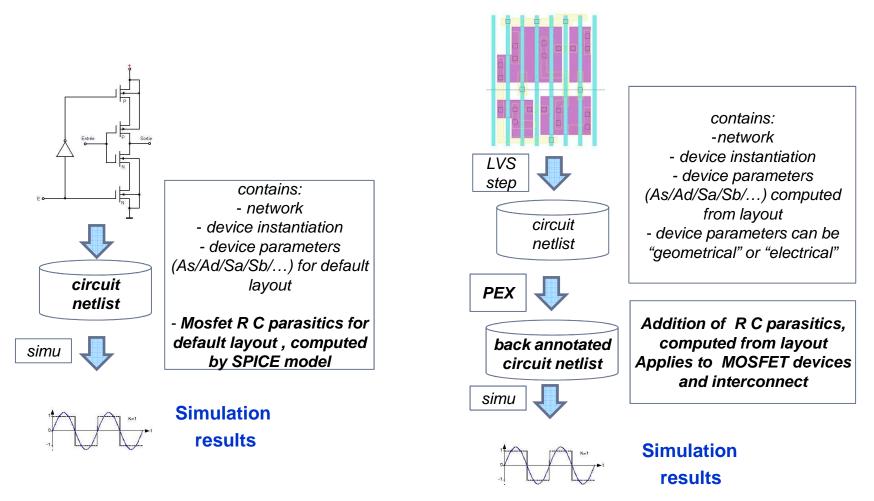

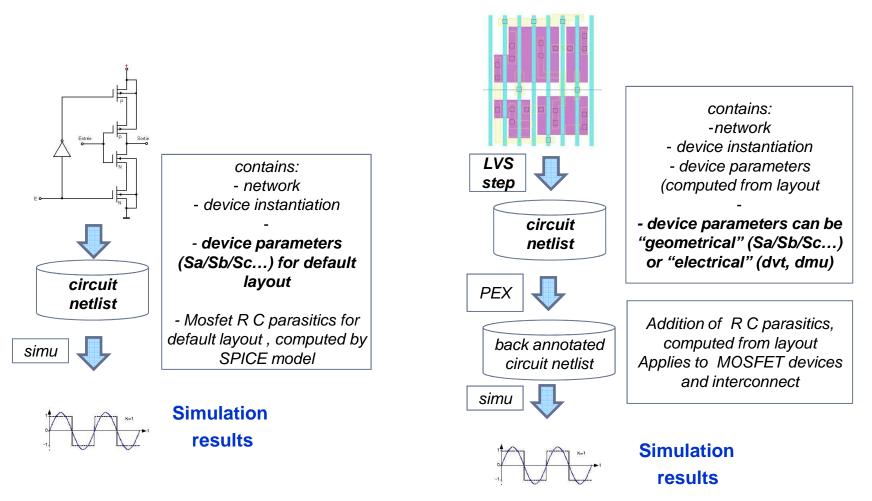

## MOSFET capacitances in real Design (Adaptative simulation flow)

- Pre-layout simulation (default layout)

- Post-layout simulation (real layout)

#### **STMicroelectronics**

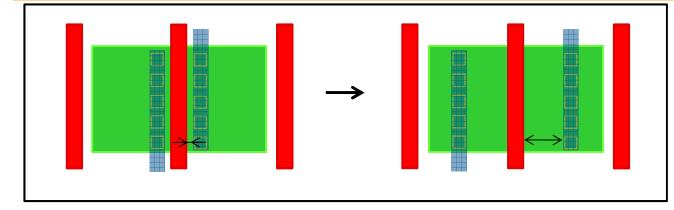

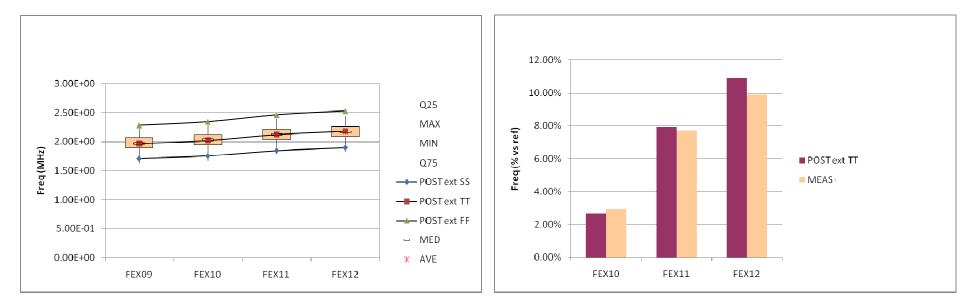

## **Verification DOEs: Impact on RO frequency**

| RO    | dgc    |

|-------|--------|

| FEX09 | Min    |

| FEX10 | X 1.43 |

| FEX11 | X 2.5  |

| FEX12 | X 5    |

•F increase vs dgc: benefit of extrinsic capacitance reduction

•Efficient CAD accuracy monitoring methodology.

## **MOSFET Parasitics vs ITRS roadmap**

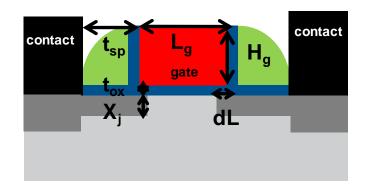

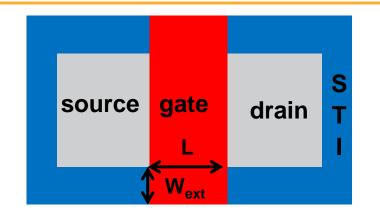

- From ITRS, we have for each year and each device structure the following parameters:

- L

- CPP (contacted gate pitch)

- t<sub>inv</sub>

- X<sub>i</sub> for Bulk devices

- **t**<sub>si</sub> for FDSOI or multigate devices

- Structural parameters are derived =>

| Parameters        | Evaluation                        |

|-------------------|-----------------------------------|

| t <sub>sp</sub>   | (CPP-L)/3                         |

| H <sub>g</sub>    | 2L                                |

| W <sub>ext</sub>  | L                                 |

| W                 | 3xCPP                             |

| dL                | L/4                               |

| t <sub>ox</sub>   | 2t <sub>inv</sub>                 |

| W                 | 3xCPP                             |

| H <sub>si</sub>   | 3xt <sub>si</sub>                 |

| FP                | t <sub>si</sub> + H <sub>si</sub> |

| N <sub>fin</sub>  | W/FP                              |

| t <sub>mask</sub> | t <sub>si</sub>                   |

• Parasitics impact have been evaluated for each year for the following devices: Bulk, FDSOI, planar DG and FinFET (J.Lacord, SSDM 2011)

TRD / STD / T2D

## **MOSFET Parasitics vs ITRS roadmap**

Bulk FET cross-section

### Bulk FET top view (wo contact)

## **MOSFET Parasitics vs ITRS roadmap**

Total Gate + Parasitics over Gate cap. Ratio

- ITRS Parasitics weight and evolution below FS simulation

- Planar DG presents a lower C<sub>tot</sub>/C<sub>gc</sub> ratio than FinFET

# **Layout Proximity effects**

- Overview

- Modeling approach

- STI example

- Modeling Accuracy dilemna

- Simulation flow

- CAD Accuracy

ŤL

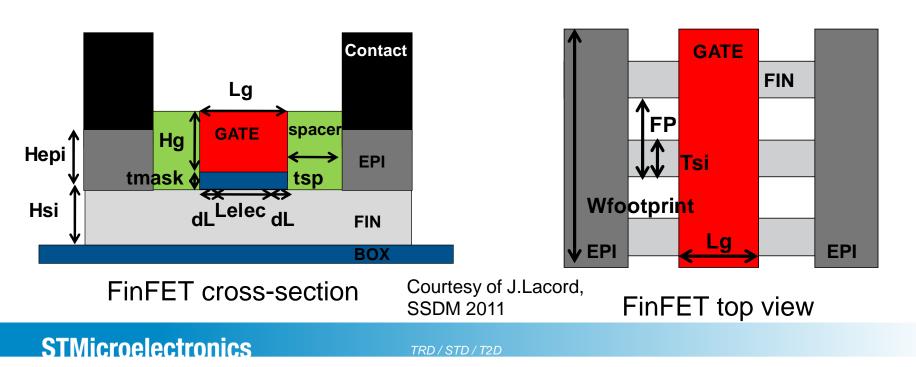

STI stress effect on Mobility (RA Bianchi, IEDM 2002)

STI stress effect on Mobility and VT (Tsuno, VLSI 2007)

60 delta overdap length (gate-to-S/D) [um] O Vth 2 (c) STI (a) Gate-STI (b) Gate space -\* Vth\_sim 50 overlap length width CESL Stress Silicid de ha Vth\_sat [mV] 1 40 measured Stress 0 SW Stress 30 -1 20 TED -2 TED 10 Vdd=1 V STI Stress STI Stress 0 00 20 40 60 80 Tsuno, VLSI Inverse of gate-STI distance [1/um] 2007

•Regular Layout: Mobility impacted by Stress, VT impacted by SD diffusity (modulated by stress)

•Handling Complex Layout in Design flow requires approximations:

•Implementation shared bw Netlisting (Geometrical parameters) and Model (Electrical parameters)

•Accuracy verification is challenging

**STMicroelectronics**

## **MOSFET Layout Proximity effects overview**

| Effect                    | Contributions                                 | Critical<br>distance                   | Post-Layout<br>Per Instance<br>parameters |    |

|---------------------------|-----------------------------------------------|----------------------------------------|-------------------------------------------|----|

| WPE                       | lon scattering on well photoresist            | >1um                                   | SCA, SCB, SCC                             |    |

| STI(LOD)                  | STI Stress<br>SD diffusion                    | 1um<br>Local                           | SA, SB                                    |    |

| STI (OD2OD)               | Litho and Etch<br>STI stress                  | Context<br>1um                         | VT and Mu correction                      |    |

| Active corner<br>rounding | Litho and Etch                                | Local                                  | Weff correction                           |    |

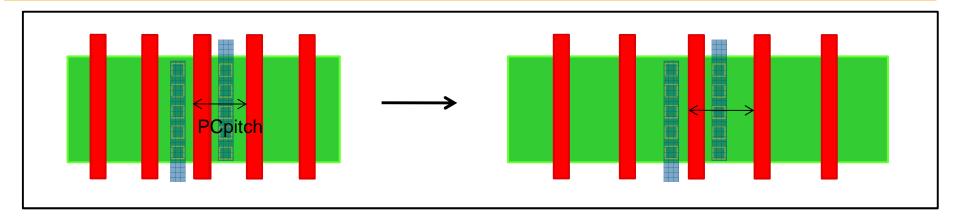

| Gate pitch                | Litho and Etch<br>CESL Stress<br>SD diffusion | Context<br>Context up to 1 um<br>Local | VT and Mu<br>correction                   |    |

| Gate corner<br>rounding   | Litho and Etch                                | Local                                  | Leff correction                           |    |

| Contacts position         | SD Rseries<br>Channel stress                  | Local                                  | Rs and Cs correction                      | WN |

| Others                    |                                               |                                        |                                           |    |

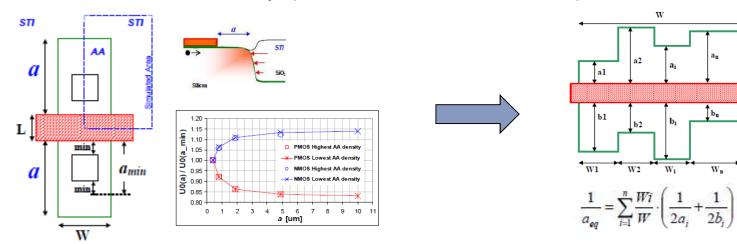

• A bunch of Design dependent effects related to distances between Well, Gate, Active, Contact layer patterns and related density context

•Different physical effects interplay; impact, amplitude are technology dependent

•Each transistor sensitivity to each effect also depends on instance W/L

TRD / STD / T2D

## **MOSFET proximity effects: Accuracy dilemna**

- A bunch of effects with 1-10% impact of performance (Low Power technology), and more (High Power technology, where Stress effect is dominant)

- Characterization dilemna: Layout DOEs

- WPE: 4W x 4L x 6 distances x 2 orientations x 2 N/P devices= 394 DUTs

- Overall about 2K DUTs per N/P device, not considering interaction between effects!

- CAD Netlisting dilemna : Post Layout extraction

- Nb Geometrical instances > 100, loss of simulation efficiency

- Pre-processing of geometrical/ electrical parameter variation through LVS: a must!

- Modeling:

- Compact modeling of all effects with interactions is not experimentally applicable

- Focus on first order layout effects and their dependence with W/L

- Monitoring of CAD + Models accuracy through test structures offering efficient test methods

Layout example

## MOSFET capacitances in real Design (Adaptative simulation flow)

- Pre-layout simulation (default layout)

- Post-layout simulation (real layout)

#### **STMicroelectronics**

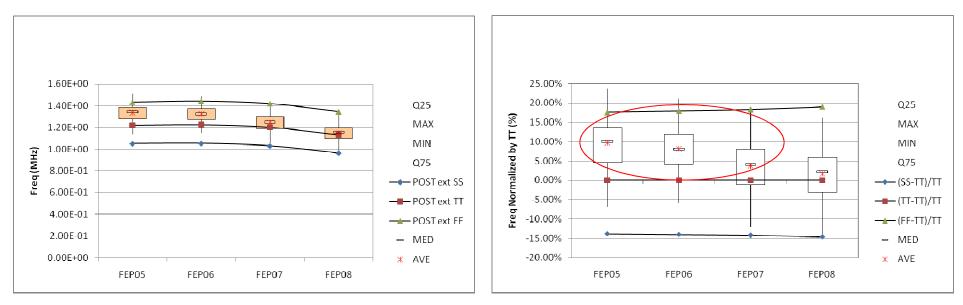

### **MOSFET Layout Proximity effects: CAD Accuracy**

Example of Monitoring Gate Pitch effects with Ring Oscillator: CAD to Silicon mismatch can be depicted

#### **STMicroelectronics**

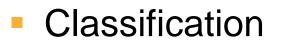

# **Process Variations/ Statistical Variability**

- Sources of variations

- Model requirements

- Impact of Global/Local Variations: RO example

- Corner vs Statistical models

# **Classification of Variations**

|                 |                  | Process                                                                                                                              | Environment                                                  | Temporal                                                                                  |  |

|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Global          |                  | <l<sub>a&gt; and <w><br/><layer thicknesses=""><br/><r>'s<br/><doping><br/><v<sub>body &gt;</v<sub></doping></r></layer></w></l<sub> | T environment<br>range<br>V <sub>dd</sub> range              | <nbti><br/>Hot electron shifts</nbti>                                                     |  |

| Local           | Syste-<br>matic  | OPC<br>Phase shift<br>Layout mediated strain<br>Well proximity                                                                       | Self-heating<br>IR drops                                     | Distribution of NBTI<br>Voltage noise<br>SOI V <sub>bodv</sub> history<br>Oxide breakdown |  |

|                 | Statis-<br>tical | Random dopants<br>Line Edge Roughness<br>Poly Si granularity<br>Interface roughness<br>High-k morphology                             |                                                              | history                                                                                   |  |

| Across-<br>chip |                  | Line width due to pattern<br>density effects                                                                                         | Thermal hot spots due<br>to non-uniform power<br>dissipation | Computational load dependent hot spots                                                    |  |

Variations Sources at Circuit scale

Classification from D.J.Frank (IBM)

Where Compact Model Extensions can help

## Variations in statistical models: sources

**Global Process**

#### Systematic Across wafer

- *Technology p*erspective: Process dependent Systematic effects

- •Design perspective: global variations

### Across Chip

#### Mask tolerance Litho/Etch

...

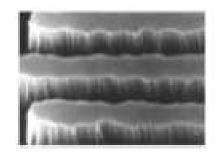

### Local Statistical

#### Line edge roughness

#### Poly Si granularity

#### **Channel dopants**

Source: University of Glasgow, Device Modeling group, A.Asenov

### **STMicroelectronics**

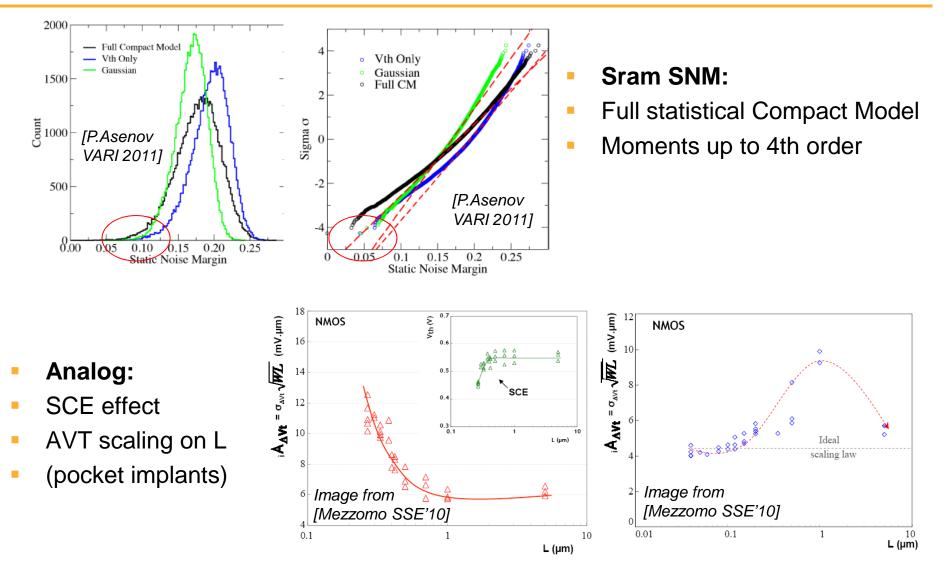

## Modeling Improvements for Local Statistical Variations (Mismatch)

#### **STMicroelectronics**

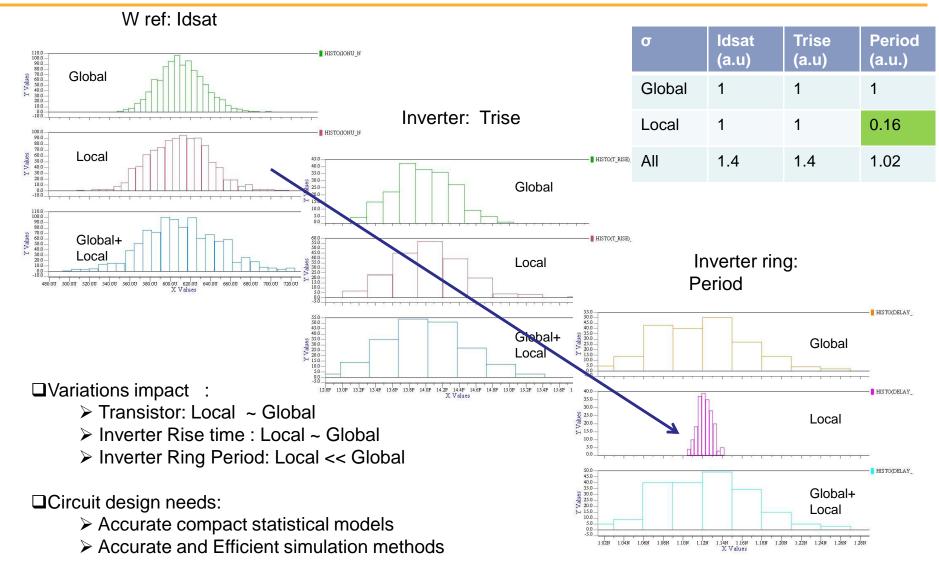

### Impact Global/Local Variations impact: RO example

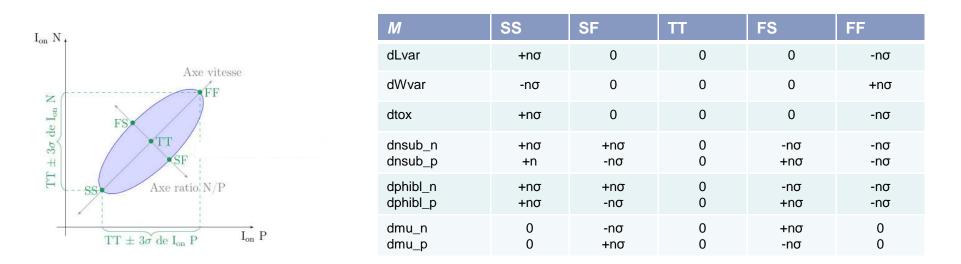

# **Corner Models vs Statistical Models**

- Principle: simulate circuit tolerance with combinations of pre-defined +/- nσ deviations of model independent parameters to minimize computational effort

- Example (PSP inputs, Speed criteria):

- Method simple and computationally efficient, but ...

- Corners are Performance specific . Ion, Ileakage, Speed, N/P ratio,...

- Suited to Global variations (Local deviations expected to average to 0 at circuit scale)

- Therefore requires validation against Statistical simulation

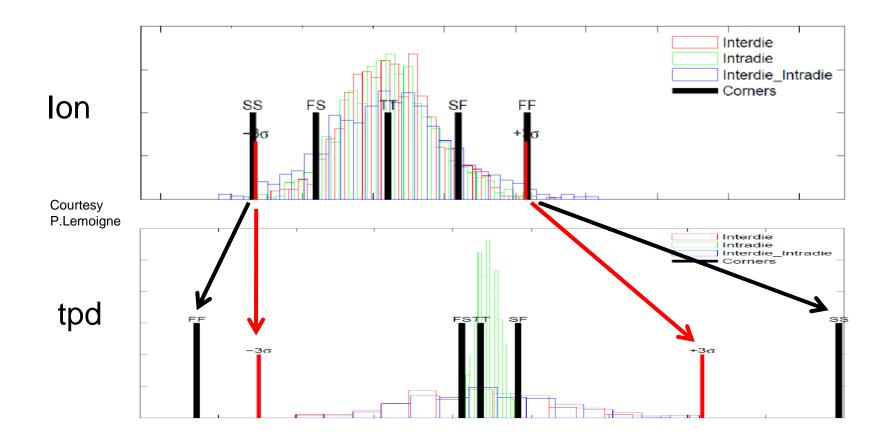

## **Corner vs Statistical Models: RO example**

$\Box$  Corners  $\Delta$ Ion ~ +/- 3 $\sigma$ ,  $\Delta$ tpd > +/- 3 $\sigma$

**STMicroelectronics**

# **Perspectives**

- New devices (FDSOI planar, Finfets)

- Methodologies

- Statistical model accuracy

- Corner model methodology

- Efficient /Accurate MC simulation

**Reliability Aware Design**

- Reliability aware design

- Reliability aware modeling

- Results: Std Cells

## **Reliability-aware design**

#### Reliability impact on circuits is a function of

- operating modes of circuits,

- operating conditions faced by devices as a combination of these modes and the various input stimuli

- □ sensitivity of the performance of the circuit in the context of its place in design hierarchy

- E.g., a small shift in differential pair could affect the product, while a big shift in transistors in a power-down control block may affect nothing

#### Design-in Reliability (DiR) =

set of methodologies and tools enabling quantitative reliability assessment at design-level

- Translate device reliability information for use by circuits

- Library reliability information is requested by system designers

- Identify potential reliability problem conditions

- Take into account the actual operating conditions of a design library

- mode, stimuli, ambient conditions

Secure without over-design

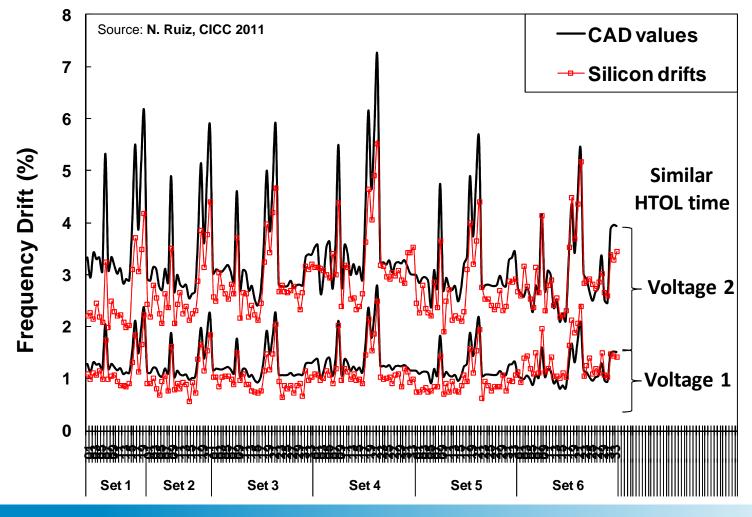

# Reliability-aware modeling – Std cells results

Reliability CAD values must be compared to drifts observed during HTOL test campaigns on library qualification testchips.

**STMicroelectronics**

# Summary

- Mosfet parasitics are performance limiting factors

- Extrinsic cap may exceed ~x2 intrinsic cap for coming device generations

- Impact of Layout effects is difficult to estimate for coming technologies (as long as impact of each individual effect is less than 10 %).

- The experimental methodology learnings to account for these effects in current technologies will help

- Statistiscal Variability has raised from an Analog concern to a limiting factor for SRAM yield (Vddmin,...)

- Both Process Variations and Statistical Variability remain concerns for modeling new devices for Low Power / High Performance applications

- Reliability aware Design is coming: requires a set of methodologies and tools enabling quantitative life-time assessment at circuit-level

- In Industry, those subjects will keep attention from the Modeling and Reliability expert communities from now and through the coming years.

**STMicroelectronics**

TRD / STD / T2D

# Acknowledgements

- Prof A.Asenov and Device Modeling Group (University of Glasgow)

- for highlights on Variability modeling and simulation

- Dr Gerard Ghibaudo (IMEP)

- for highlights on Variability characterization and modeling

- EU ENIAC Modern project

- for supporting development of solutions for Statistical Variability and Reliability

- ST team :

- David Hoguet, Jean-Claude Marin, Vincent Quenette, Joris Lacord, Vincent Huard, N. Ruiz, E. Pion, F.Cacho, Clément Charbuillet, P.Lemoigne