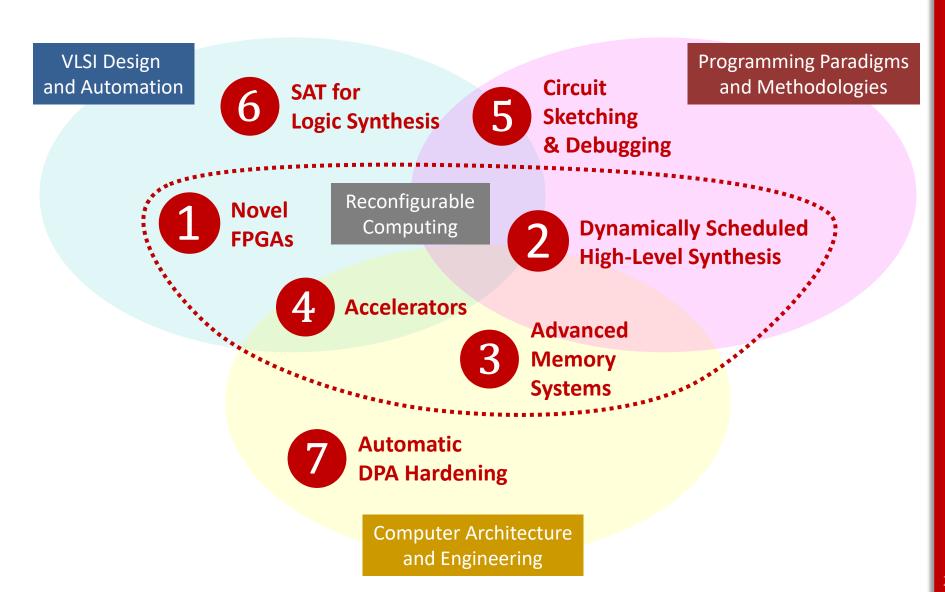

## Research at LAP

Paolo lenne

**Processor Architecture Lab**

### **Current Research**

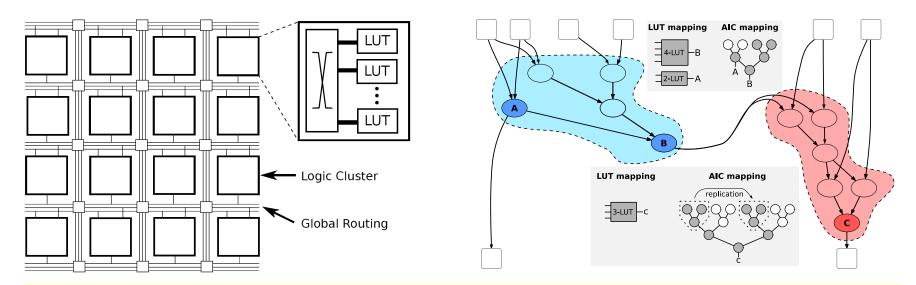

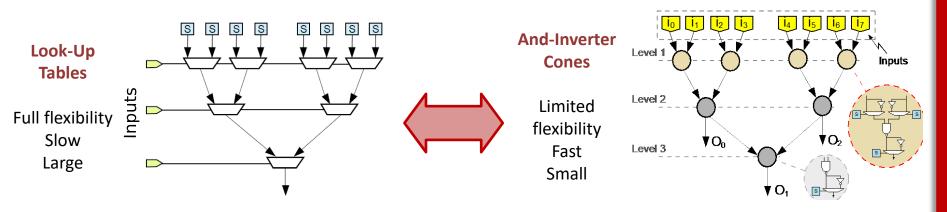

## Rethinking FPGA Architectures

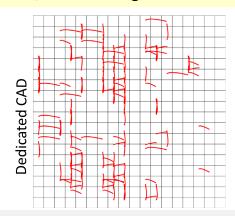

Idea: Replace Look-Up Tables with And-Inverter Cones (AICs) as basic logic blocks Goal: Increase device efficiency by renouncing some excess of flexibility

Jiang, Zgheib, Lin, Novo, Huang, L. Yang, H. Yang, and Ienne. *A Technology Mapper for Depth-Constrained FPGA Logic Cells*. FPL 2015 Zgheib, Yang, Huang, Novo, Parandeh-Afshar, Yang, and Ienne. *Revisiting And-Inverter Cones*. FPGA 2014 Parandeh-Afshar et al. Rethinking FPGAs: *Elude the flexibility excess of LUTs with And-Inverter Cones*. FPGA 2012 Best Paper Award

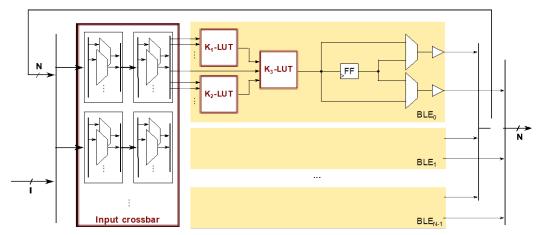

## 1 Exploring FPGA Architectures

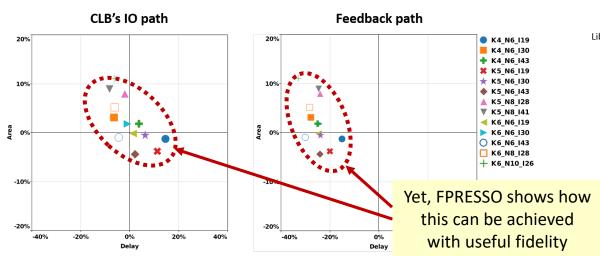

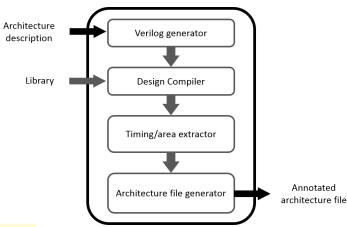

Problem: To study FPGA architectures, you need good retargetable FPGA toolsets (synthesis, mapping, P&R), such as VTR, but you also need good models of the transistor-level primitives (LUTs, crossbars, novel logic elements) and of their combinations

Idea: Leverage a common standard-cell VLSI flow to pick and optimize transistor-level primitives and to produce accurate models for the complete architectures

**Difficulties:** (1) Standard cells are not designed the same ways FPGAs circuitry is and (2) VLSI tools are not built for this purpose

fpresso.epfl.ch

Zgheib, Lortkipanidze, Owaida, Novo, and Ienne. FPRESSO: Enabling Express Transistor-level Exploration of FPGA Architectures. FPGA 2016 Best Paper Award Zgheib and Ienne. Evaluating FPGA Clusters under Wide Ranges of Design Parameters. FPL 2017 Best Paper Award Nominee

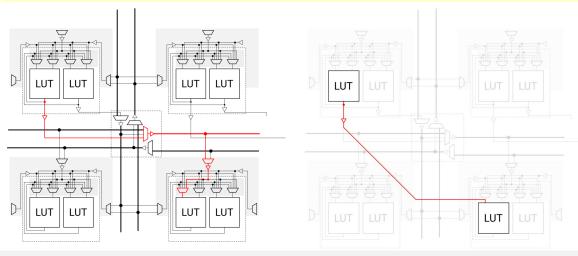

### Efficient FPGA Interconnect

**Problem:** FPGA interconnect is highly programmable, to be able to support a large number of user designs; this negatively impacts its performance. **Can we improve the interconnect?**

Idea: Introduce fast and cheap direct connections

Challenge: Where to insert them so that many user designs can benefit from them and others are not excessively damaged?

Nikolić, Zgheib, and Ienne. Straight to the Point: Intra- and Intercluster LUT Connections to Mitigate the Delay of Programmable Routing. FPGA 2020

Problem: To effectively use direct connections, new CAD algorithms are needed

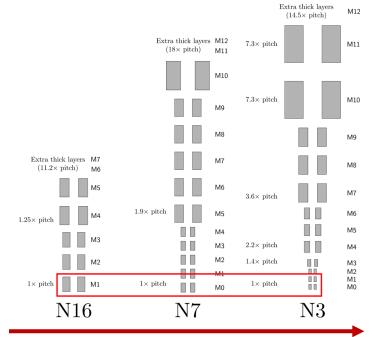

## 1 FPGAs in Scaled Technologies

**Problem:** Interconnect delays scale poorly (R and C grow quickly and wires become "slower")

Idea: Quantify the impact of technology scaling on FPGA performance and derive ways to mitigate it

**Challenge:** Devise precise enough models to capture the impact, but simple enough for architectural exploration

Newer technology nodes

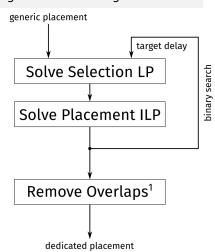

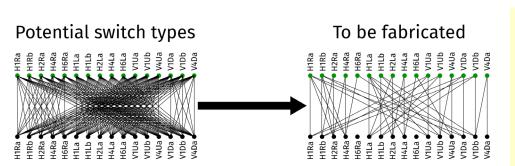

**Problem:** Complex influence of technology scaling on FPGA performance calls for effective automation of exploration of aspects of FPGA architecture insufficiently explored before

Idea: Leverage the algorithm of the FPGA router to let it decide what needs to be fabricated

## **Dynamically Scheduled HLS**

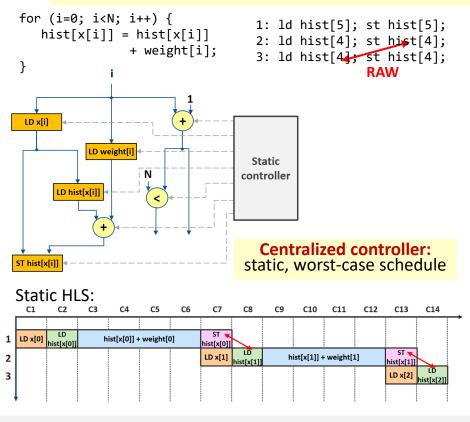

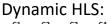

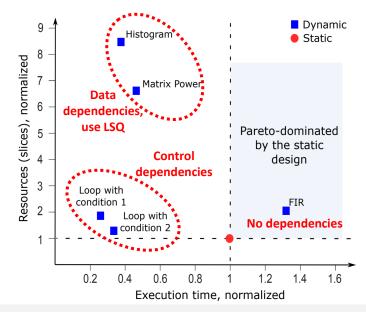

**Problem:** Current HLS tools produce **statically scheduled** circuits

dynamatic.epfl.ch

- Control and data dependencies degrade pipeline performance

- Worst-case schedule when dependency analysis cannot provide conclusive information

- In general, same limitations as VLIW processors (good for regular DSP applications, bad otherwise)

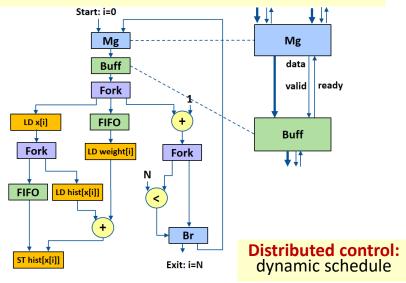

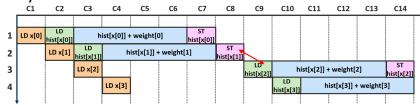

Idea: Create dynamically scheduled circuits where operations are executed as the operands are ready

Control and data dependencies are resolved on-the-fly

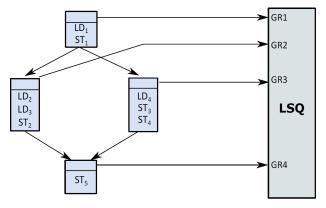

## 2 An Out-of-Order Memory Interface for Spatial Computing

Problem: Conventional Load-Store Queue allocation policy is not suitable for spatial computing

- In a processor, decoding conveys the correct sequential order of requests at the memory interface

- Spatial circuits do not have instructions or a program order

BB1: LD, ST

LSQ

LD weight

LD hist

ST hist

Memory

Groups correspond to basic blocks in HLS: all accesses in a basic block are going to take place if the control flow enters the basic block

**Idea:** Allocate **groups of memory accesses** depending on the control flow of the application

- Groups: sequences of accesses which are statically predefined

- If one access of a group executes, all other accesses belonging to the same group will eventually execute

### Static vs. dynamic scheduling:

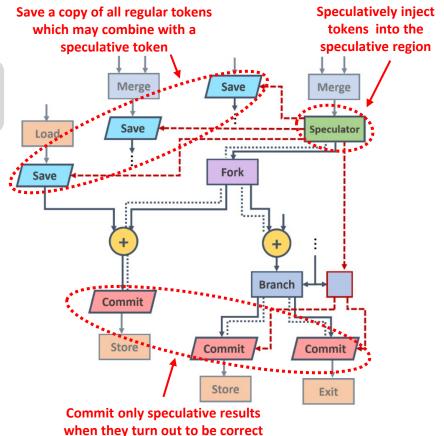

### **Speculation in Dataflow Circuits**

**Challenge:** Execute certain operations before it is known that they are correct or required

- Increase parallelism in loops where the condition takes long to compute

- Improve performance of circuits limited by potential memory dependencies

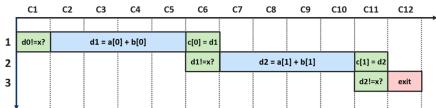

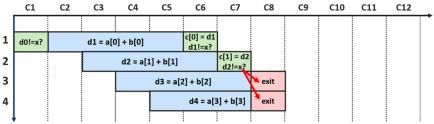

float d = 0.0; x = 100.0; int i = 0; while (d < x) do { d = a[i] + b[i]; c[i] = d; i++; } 0: a[0]=50.0; b[0]=30.0 1: a[1]=40.0; b[1]=40.0 2: a[2]=50.0; b[2]=60.0  $\rightarrow$  exit

Nonspeculative schedule: conservatively wait for loop condition

Speculative schedule: tentatively start another loop iteration

**Idea:** Contain **speculation in a region** of the circuit delimited by special components

- Issue speculative tokens (pieces of data which might or might not be correct)

- Squash and replay in case of misspeculation

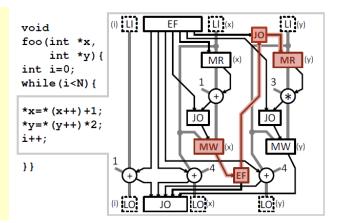

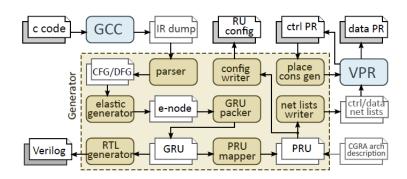

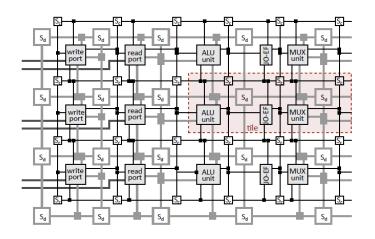

# An Elastic Coarse Grain Reconfigurable Array

#### **Elastic circuits**

mimic the dynamic processing of asynchronous circuits in a synchronous context and provide controlflow synchronization primitives (EB, EF, MG, JO, BR...)

Problem: Most CGRAs are statically scheduled like *VLIWs*. (1) It is hard to develop efficient schedules and (2) such schedules are very sensitive to latency variability

Idea: An array of elastic components interconnected by an FPGA-like routing network → the superscalar of the CGRAs!

A complete tool chain to optimize, map, place, and route C programs on the Elastic CGRA

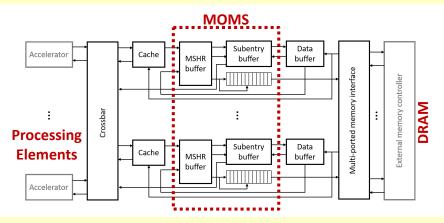

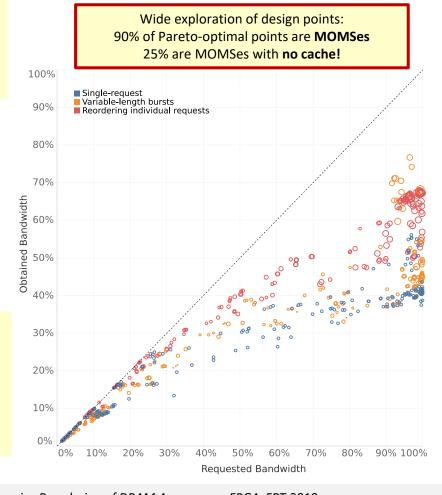

# Miss-Optimized Memory Systems (MOMSes)

Problem: Effective DRAM bandwidth is more than one order of magnitude smaller than peak bandwidth when accesses from accelerators are irregular and narrow (e.g., sparse linear algebra, graph traversal)

Idea: Instead of trying to increase the hit rate (with costly caches), focus on better handling misses. That is, build nonblocking caches with 1000's of Miss Status Holding Registers (MSHRs) instead of the usual 10-20.

**Challenge:** How to implement efficiently the associative structure needed for 1000's of MSHRs?!

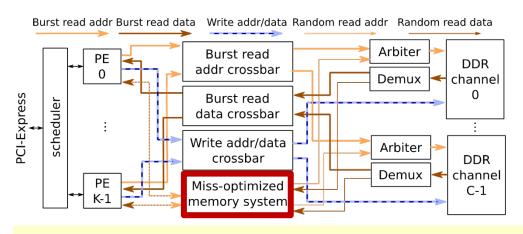

## Large-Scale Graph Processing on FPGAs with MOMS

**Problem:** Show that MOMSes can be useful for **practical FPGA accelerators in the cloud**

Intuition: No need for software defined data movement, dynamic data movement ("caches") can be made to work if designed appropriately

|                     | Platform | Ext. mem. bandwidth | Power  |

|---------------------|----------|---------------------|--------|

| This work, FabGraph | FPGA     | 64 GB/s             | 23 W   |

| Gunrock             | GPU      | 900 GB/s            | 300 W* |

| Ligra, GraphMat     | CPU      | 233 GB/s            | 224 W  |

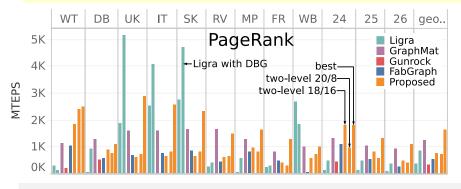

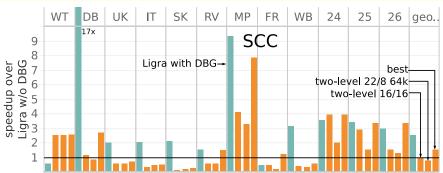

#### **Results:**

- PageRank:

- 3x faster than state-of-the-art on FPGA

- PageRank, Strongly Connected Components:

- competitive with state-of-the-art on CPU and GPU

- 1.1x to 15.3x more bandwidth and power efficiency

- Single Source Shortest Path

- competitive with SotA on CPU

(→ higher bandwidth and power efficiency)

- GPU is much faster but can only handle the smallest benchmarks!

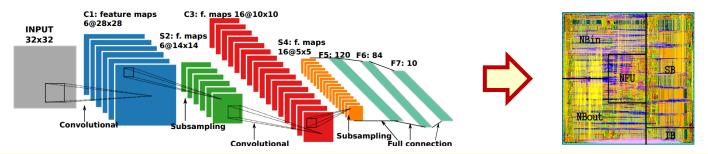

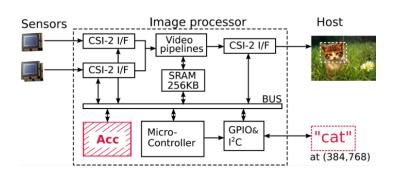

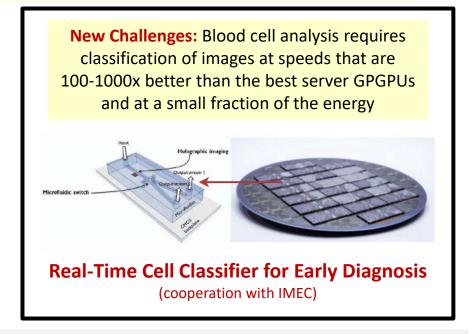

# 4 Accelerating CNNs for Vision and Classification

**Problem:** Convolutional and Deep Neural Networks (CNNs and DNNs) are extremely effective for some classification tasks but are terribly computationally demanding and poorly suited for GPGPUs

Idea: Design a programmable accelerator suitable for integration in a standard embedded camera chipset (no DRAM, limited SRAM, etc.)

Result: About 30x more performance than a typical GPU for less than 1/4500th of the energy

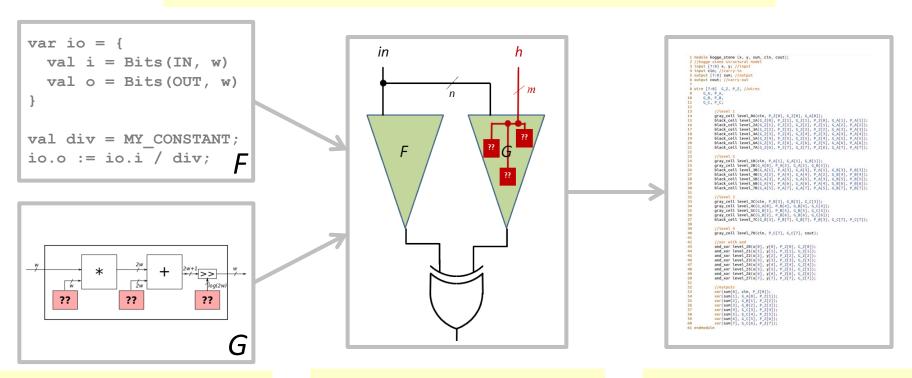

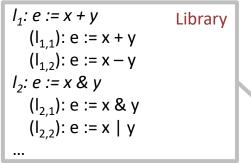

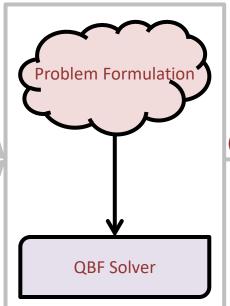

## Improving Circuit Design with a "Fill-in-the-Blank" EDA Tool

**Problem:** Humans are good at big-picture design, but not the details **Idea:** Let software build the circuit from a designer's sketch

Designer specifies naïve functionality and provides incomplete optimized RTL design

Software tool solves a problem to find how to fill in *holes* left by the designer in the optimized design

Designer gets back completed, optimized, guaranteed-correct circuit in RTL

## **5** Automated Circuit Debugging

**Problem:** Debugging is expensive, even though the same bug types appear often.

Idea: Instrument circuits with common fixes. Solver finds if some combination actually works.

(instrumentation)

...

else if(op == OP\_SH)

o=shift(b,a[5:0]);

...

RTL Source

Buggy circuit design and library of common RTL errors provided to software suite

(interpretation)

rtl/alu.v@29.11 Signal 'b' should be 'a'

rtl/alu.v@29.13 Signal 'a' should be 'b'

Software tools determine suspicious RTL, apply matching error rules, and find fixing combination(s)

Designer gets back *meaningful* error diagnosis exactly describing the problem and necessary fix

## 6 SAT Methods for Logic Synthesis

|    | $x_1$ | $x_2$ | $x_3$ | $x_4$ | f |

|----|-------|-------|-------|-------|---|

| 1  | 0     | 0     | 0     | 1     | 1 |

| 5  | 0     | 1     | 0     | 1     | 1 |

| 10 | 1     | 0     | 1     | 0     | 1 |

| 11 | 1     | 0     | 1     | 1     | 1 |

| 13 | 1     | 1     | 0     | 1     | 1 |

smallest SAT assignment

greatest SAT assignment

### **Fast Generation of LEXSAT Assignments**

Problem: Generate a satisfiable assignment with the smallest (or greatest) integer value for a given variable order (a LEXSAT assignment)

Idea: Use the concept of the binary search algorithm to determine the LEXSAT assignment

Results: 2.4x faster generation of a single assignment, 6.3x faster generation of multiple assignments

**Application 1:** <u>SAT-based</u> computation of canonical Sum of Products (SOPs)

LEXSAT enables generating minterms in a deterministic order

**Application 2:** Heuristic NPN classification for large functions (with up to 194 variables)

LEXSAT enables comparing the integer value of two truth tables

Petkovska, Mishchenko, Soeken, De Micheli, Brayton, and Ienne. Fast Generation of Lexicographic Satisfiable Assignments: Enabling Canonicity in SAT-based Applications. ICCAD 2016

Soeken, Mishchenko, Petkovska, Sterin, Ienne, Brayton, and De Micheli. *Heuristic NPN Classification for Large Functions Using AIGs and LEXSAT*. SAT 2016

Best Paper Award Nominee

Petkovska, Mishchenko, Soeken, De Micheli, Brayton, and Ienne. Fast Generation of Lexicographic Satisfiable Assignments: Enabling Canonicity in SAT-based Applications. IWLS 2016 Best Student Paper Award Nominee

Petkovska, Mishchenko, Novo, Owaida, and lenne. Progressive Generation of Canonical Sums of Products Using a SAT Solver. IWLS 2016

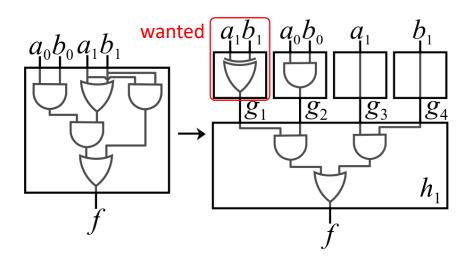

# 6 Constrained Interpolation for Guided Logic Synthesis

Problem: Craig interpolation reconstructs a target function f using random base functions from the given set G and often omits some wanted base functions (up to 60%)

**Carving Interpolation** is a novel method to impose a base function  $g_i$

$$f = h(g_1, \dots, g_n) = g_i \cdot I_{g_i} + \overline{g_i} \cdot I_{\overline{g_i}}$$

Omits only 0.15% of the wanted base functions

f is reconstructed using a Shannon expansion of two constrained interpolants built for  $g_i = 1$  and  $g_i = 0$ , respectively

Useful for ECO and some logic synthesis algorithms

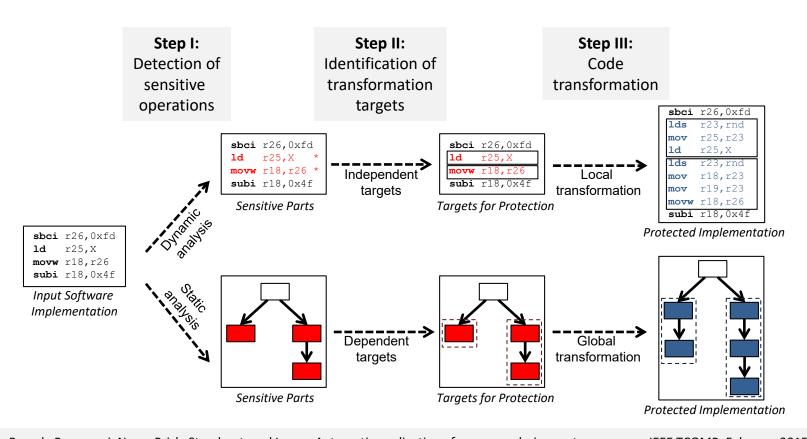

# Automated Side-Channel Vulnerability Discovery and Hardening

**Goal**: <u>Detect</u> the sensitive parts of a given hardware/software implementation against side-channel attacks and <u>protect</u> these parts using proper countermeasures

## Selected Not So Recent Topics

VLSI Design and Automation

Programming Paradigms and Methodologies

Verma. Pre-Synthesis Optimization of Arithmetic Circuits. EPFL Thesis 2010.

EDAA Outstanding Dissertation Award 2010 and Patrick Denantes Memorial Award 2011

Verma, Brisk, and Ienne. Iterative Layering: Optimizing arithmetic circuits by structuring the information flow. ICCAD 2009

Verma, Brisk, and Ienne. Progressive decomposition: A heuristic to structure arithmetic circuits. DAC 2007. Best Paper Award Nominee

Verma and Ienne. Improving XOR-dominated arithmetic circuits by exploiting dependencies between operands. ASPDAC 2007. Best Paper Award Nominee

## Improving FPGAs for Datapaths

Stojilović, Novo, Saranovac, Brisk, and Ienne. Selective flexibility: Creating domainspecific reconfigurable arrays. IEEE TCAD 2013

Huang, Ienne, Temam, Chen, and Wu. Elastic CGRAs. FPGA 2013

Parandeh-Afshar, Brisk, and Ienne. Exploiting fast carry-chains of FPGAs for

designing compressor trees. FPL 2009. Best Paper Award

Cevrero, Athanasopoulos, Parandeh-Afshar, Verma, Brisk, Nicopoulos, Attarzadeh

Niaki, Gurkaynak, Leblebici, and Ienne. Field programmable compressor trees:

Acceleration of multi-input addition on FPGAs. ACM TRETS 2009

Jimenez, Novo, and Ienne. Libra: Software controlled cell bitdensity to balance wear in NAND flash. ACM TECS, March 2015

Jimenez, Novo, and Ienne. Wear unleveling: Improving NAND flash lifetime by balancing page endurance. FAST 2014

Jimenez, Novo, and Ienne. Phoenix: Reviving MLC blocks as SLC to extend NAND flash devices lifetime. DATE 2013

Jimenez, Novo, and Ienne. Software controlled cell bit-density to improve NAND flash lifetime. DAC 2012

Computer Architecture and Engineering

## Selected Even Less Recent Topics

VLSI Design and Automation

Programming Paradigms and Methodologies

Worm. Robust checkers for self-calibrating designs. EPFL Thesis 2006.

#### **EDAA Outstanding Dissertation Award 2006**

Worm, Thiran, and lenne. *Designing robust checkers in the presence of massive timing errors.* IOLTS 2006

Worm, lenne, Thiran, and De Micheli. *On-Chip self-calibrating communication techniques robust to electrical parameter variations*. IEEE D&T 2004

## **Customizable Processors**

Kluter, Burri, Brisk, Charbon, and Ienne. Virtual Ways: Efficient coherence for architecturally visible storage in automatic instruction set extensions.

HiPEAC 2010. Best Paper Award Nominee

Verma, Brisk, and Ienne. Rethinking custom ISE identification: A new processor agnostic method.

CASES 2007. Best Paper Award

Biswas, Dutt, Ienne, and Pozzi. Automatic

2006. **Best Paper Award Nominee**Atasu, Pozzi, and Ienne. *Automatic Application-Specific Instruction-Set Extensions under Microarchitectural Constraints*. DAC 2003.

identification of application-specific functional

units with architecturally visible storage. DATE

**Best Paper Award**

## Portable Reconfigurable Accelerators

Vuletić, Pozzi, and Ienne. Virtual memory window for application-specific reconfigurable coprocessors. IEEE TVLSI 2006

Dubach, Vuletić, Pozzi, and Ienne. Enabling unrestricted automated synthesis of portable hardware accelerators for virtual machines. CODES 2005

Vuletić, Pozzi, and Ienne. Seamless hardware-software integration in reconfigurable computing systems. IEEE D&T 2005

Vuletić, Pozzi, and Ienne. Dynamic prefetching in the virtual memory window of portable reconfigurable coprocessors. FPL 2004

Computer Architecture and Engineering