# Quantum perspectives in computing, sensing, communication, and metrology **Edoardo Charbon** EPFL, Lausanne, Switzerland

# **Aknowledgements**

Simone Frasca Pascal 't Hart Jiang Gong Harald Homulle Andrea Ruffino Yatao Peng M. Fernando Gonzalez-Zalba Fabio Sebastiano Masoud Babaie Daniele Faccio Andrew Dzurak

## **Outline**

- Quantum computing (2 periods)

- 2. Cryogenic electronics (2 periods)

## Available in a future class:

- 3. Quantum algorithms (2 periods)

- Quantum imaging and communications (1 period)

- 5. Quantum metrology (2 periods)

# **Suggested Reading**

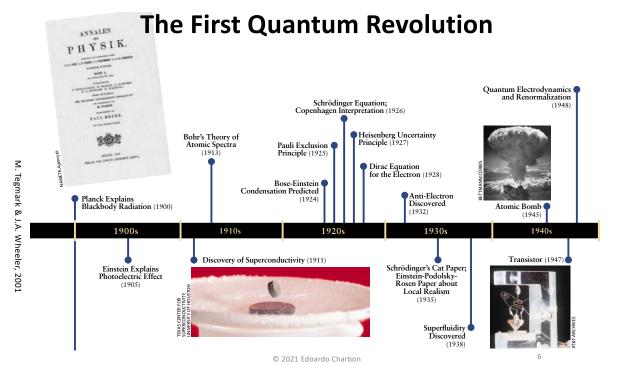

# The First Quantum Revolution

# Weird Quantum Properties:

**Superposition & Entanglement**

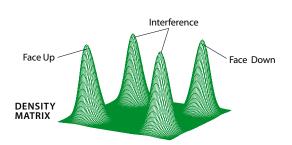

# **Superposition**

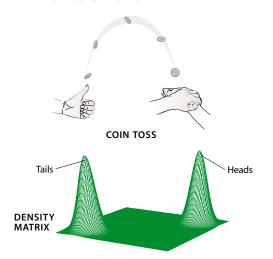

### CLASSICAL UNCERTAINTY

### **QUANTUM UNCERTAINTY**

### **COHERENT SUPERPOSITION**

# **Coherence / Decoherence**

# **Entanglement**

<u>Definition:</u> two particles are entangled if the quantum state of one particle cannot be described independently from the quantum state of the other particle.

<u>Intuition:</u> measuring the quantum state of one particle implies knowledge of the quantum state (e.g. momentum, spin, polarization, etc.) of the other entangled particle using the same projection.

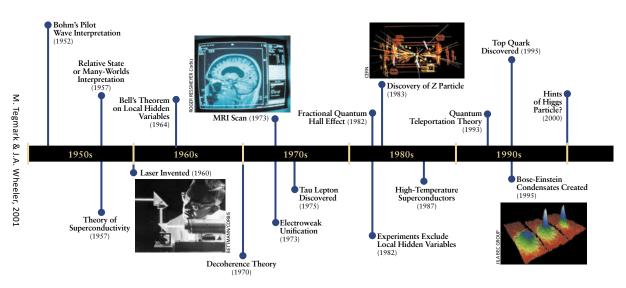

# **The Second Quantum Revolution**

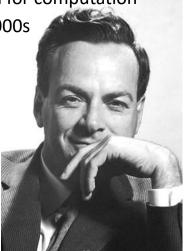

• Spearheaded by many, in primis Richard Feynman

Proposal to use of entanglement and superposition for computation

• Fundamentals and theory developed in the 1980-2000s

There is plenty of space at the bottom

- Richard Feynman

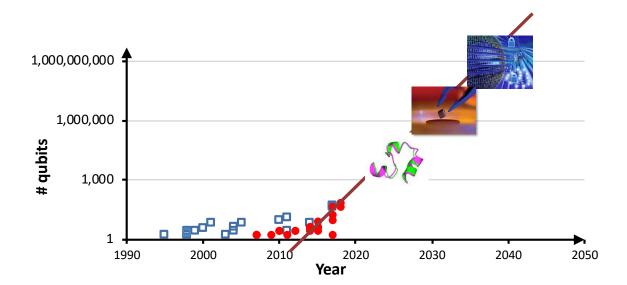

# The Promise of Quantum Computing

Energy

Room-temperature superconductivity

Source: L. Vandersypen, ISSCC 2017

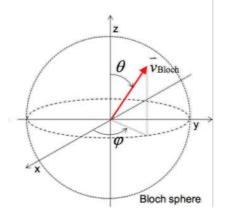

# **Quantum Bit (Qubit)**

$$|\psi\rangle = \alpha_0 |0\rangle + \alpha_1 |1\rangle$$

- Superposition

- Entanglement

# **The Power of Superposition**

| 1 qubit  | 2 states              |

|----------|-----------------------|

| 2 qubits | 4 states              |

| ·        |                       |

| N qubits | 2 <sup>N</sup> states |

40 qubits: 10<sup>12</sup> parallel operations

300 qubits: more than the atoms in the universe

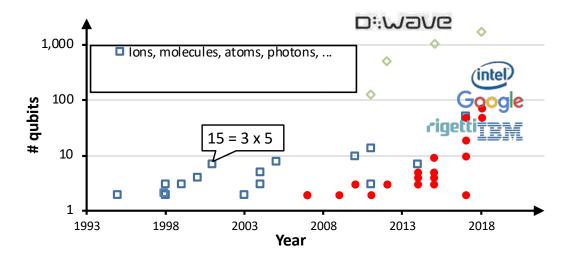

## State-of-the-Art

# **How Far Are We from Something Useful?**

# **Quantum Supremacy or Quantum Advantage**

Quantum supremacy is the potential ability of quantum computing devices to solve problems that classical computers practically cannot.

[Wikipedia]

# Google claims to have reached quantum supremacy (Financial Times)

Report on a an accepted paper to a peer-reviewed publication

# **Solid-state Qubit Implementations Today**

- Based on superconducting qubits

- First multi-qubit chips announced

- Freely available qubits on line

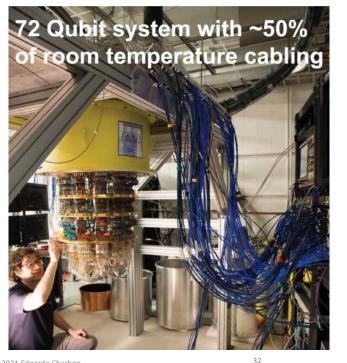

72-qubit chip announced

Total 22 qui foote

Total 22 qui foote

Total 32 qui foote

T

Source: Tristan Meunier

16 Qubits online version

50 qubit chip announced

# **Solid-state Qubit Implementations Today**

Semiconductor-superconductor hybrids

Impurities in diamond or silicon

ource: L. Vandersypen, 2017

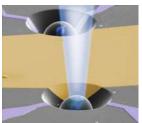

# **Qubits are Fragile**

- Environment can cause decoherence due to dephasing and relaxation

- Fidelity

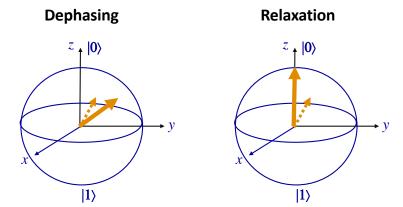

# **Qubit Transition from |0> to |1>**

© Jeroen van Dijk

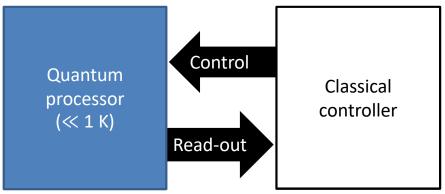

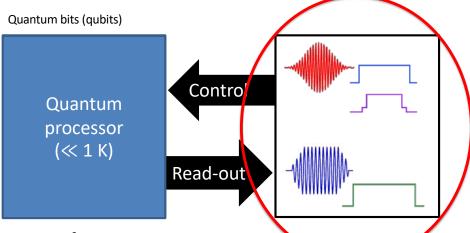

# **Interfacing Qubits with Classical World**

Quantum bits (qubits)

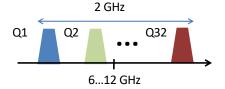

• Carrier frequency: 100 MHz – 15 GHz, 70 GHz

Pulses: 10 – 100 ns

# **Interfacing Qubits with Classical World**

- Carrier frequency: 100 MHz 15 GNz, 70 GHz

- Pulses: 10 100 ns

- Readout techniques for spin qubits: ESR, EDSR

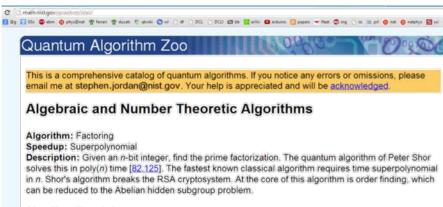

# **Status of Quantum Algorithms**

Algorithm: Discrete-log Speedup: Superpolynomial

**Description:** We are given three n-bit numbers a, b, and N, with the promise that  $b = a^s \mod N$  for some s. The task is to find s. As shown by Shor [82], this can be achieved on a quantum computer in poly(n) time. The fastest known classical algorithm requires time superpolynomial in n. By similar

~50 algorithms with quantum speedup, but most people know 2.

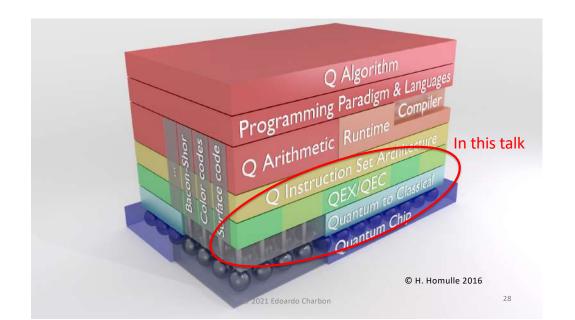

# **Quantum Computing Stack**

# Quantum Computer Architecture

# A Real-life Quantum Computer

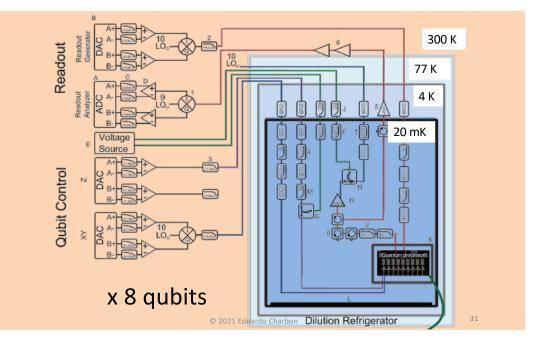

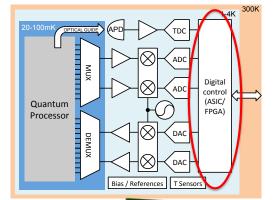

# **Today's Solution**

Image: Google Bristlecone. Taken from: J.C. Bardin et al., "An Introduction to Quantum Computing for RFIC Engineers", RFIC Symposium 2019

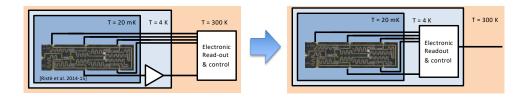

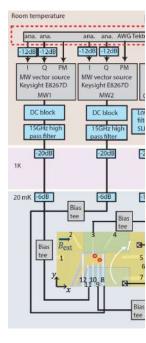

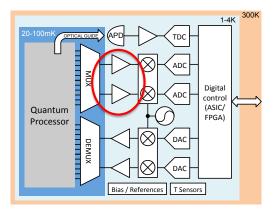

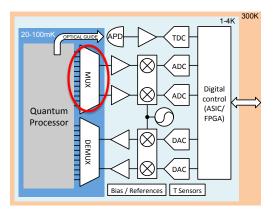

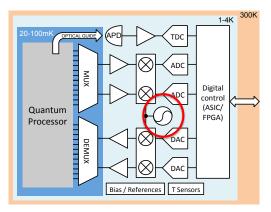

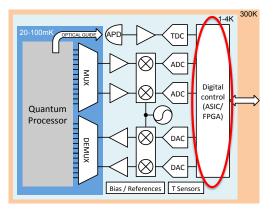

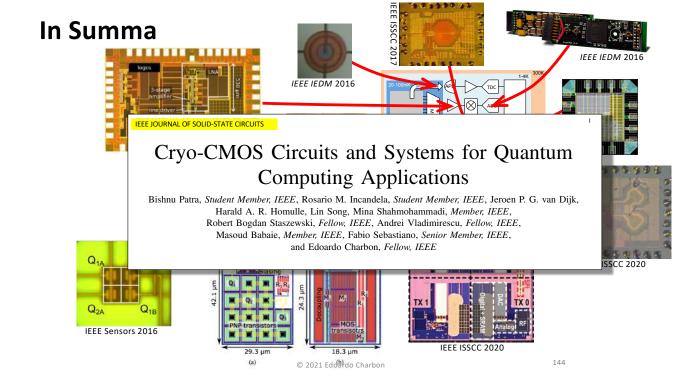

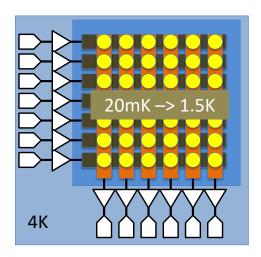

# **Our Proposed Solution**

## Proposed solution

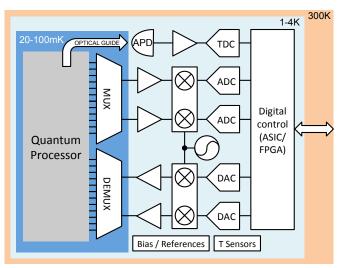

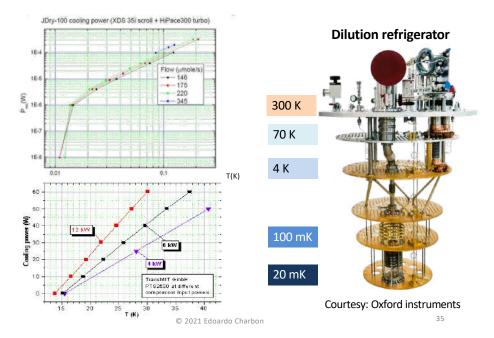

- Electronics at 4 K

- Only connections to 4 K to 20 mK are needed

## Ultimate solution

- Qubits at 4 K

- Monolithic integration

## **Electronic Readout & Control**

E. Charbon et al., IEDM 2016

# **Cooling Power Issue**

# **Scalability Issue**

| • | Noise budget                          | .< 0.1nV/√Hz |

|---|---------------------------------------|--------------|

| • | Power budget (for scalability)        | << 2mW/qubi  |

| • | Physical dimensions (for scalability) | 30nm         |

| • | Bandwidth (for multiplexing)          | 1-12GHz      |

| • | Kick-back avoidance                   |              |

2. Cryogenic Electronics

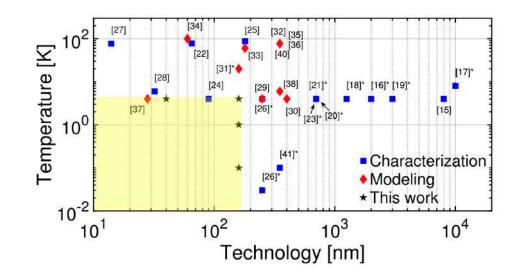

# Transistor Modeling at Deep Cryogenic

**Temperatures**

# **CMOS Modeling: Important Parameters**

## **CMOS Modeling: History**

R.M. Incandela et al., ESSDERC 2017 R.M. Incandela et al., J. of EDS 2018

- [16] H. Hanamura et al., "Operation of bulk CMOS devices at very low temperatures," IEEE J. Solid-State Circuits, vol. 21, no. 3, pp. 484–490, Jun. 1986. doi: 10.1109/JSSC 1986.1052555.

- [17] F. Balestra, L. Audaire, and C. Lucas, "Influence of substrate freeze-out on the characteristics of MOS transistors at very low temperatures," *Solid State Electron.*, vol. 30, no. 3, pp. 321–327, Mar. 1987. doi: 10.1016/9038-110187/90190-0.

- [18] L. Deferm, E. Simoen, and C. Claeys, "The importance of the internal bulk-source potential on the low temperature kink in NMOSTs," *IEEE Trans. Electron Devices*, vol. 38, no. 6, pp. 1459–1466, Jun. 1991, doi: 10.1109/16.81639.

- [19] E. Simoen, B. Dierickx, and C. L. Claeys, "Low-frequency noise behavior of Si NMOSTs stressed at 4.2 K," *IEEE Trans. Electron Devices*, vol. 40, no. 7, pp. 1296–1299, Jul. 1993, doi: 10.1109/16.216435.

- [20] E. Simoen and C. Claeys, "Impact of CMOS processing steps on the drain current kink of NMOSFET's at liquid helium temperature," *IEEE Trans. Electron Devices*, vol. 48, no. 6, pp. 1207–1215, Jun. 2001, doi: 10.1109/16.925249.

- [21] E. Simoen et al., "Impact of irradiations performed at liquid helium temperatures on the operation of 0.7 μm CMOS devices and readout circuits," in Proc. Radiat. Effects Compon. Syst. (RADECS), 2003, pp. 369–375.

- [22] A. Siligaris et al., "High-frequency and noise performances of 65-nm MOSFET at liquid nitrogen temperature," IEEE Trans. Electron Devices, vol. 53, no. 8, pp. 1902–1908, Aug. 2006, doi: 10.1109/TED.2006.877872.

- [23] Y. Creten, P. Merken, W. Sansen, R. Mertens, and C. van Hoof, "A cryogenic ADC operating down to 4.2K," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2007, pp. 468–616. doi: 10.1109/ISSCC.2007.373497.

- [24] S.-H. Hong et al., "Low-temperature performance of nanoscale MOSFET for deep-space RF applications," IEEE Electron Device Lett., vol. 29, no. 7, pp. 775–777, Jul. 2008, doi: 10.1109/LED.2008.2000614.

- [25] G. De Geronimo et al., "Front-end ASIC for a liquid argon TPC," in Proc. IEEE Nuclear Sci. Symp. Med. Imag. Corf., vol. 58. Knoxville, TN, USA, Oct. 2010, pp. 1658–1666, doi: 10.1109/NSSMIC.2010.5874057.

- [26] S. R. Ekanayake, T. Lehmann, A. S. Dzurak, R. G. Clark, and A. Brawley, "Characterization of SOS-CMOS FETs at low temperatures for the design of integrated circuits for quantum bit control and readout," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 539–547, Feb. 2010, doi: 10.1109/TED.2009.2037381.

- [27] M. Shin et al., "Low temperature characterization of 14nm FDSOI CMOS devices," in Proc. 11th Int. Workshop Low Temp. Electron. (WOLTE), Grenoble, France, Jul. 2014, pp. 29–32, doi: 10.1109/WOLTE.2014.6881018.

- [28] A. H. Coskun and J. C. Bardin, "Cryogenic small-signal and noise performance of 32nm SOI CMOS," in Proc. IEEE MTT-S Int. Microw. Symp. (IMS), Tampa, FL, USA, Jun. 2014, pp. 1–4, doi: 10.1109/MWSYM.2014.6848614.

- [29] Y. Feng, P. Zhou, H. Liu, J. Sun, and T. Jiang, "Characterization and modelling of MOSFET operating at cryogenic temperature for hybrid superconductor-CMOS circuits," *Semicond. Sci. Technol.*, vol. 19, no. 12, pp. 1381–1385, Oct. 2004, doi: 10.1088/0268-1242/19/12/009.

- [30] A. Akturk et al., "Impact ionization and freeze-out model for simulation of low gate bias kink effect in SOL-MOSFETs operating at liquid He temperature," in Proc. Conf. Simular. Semicond. Process. Devices (SISPAD), Sep. 2009, pp. 1–4, doi: 10.1109/ISISPAD.2009.5290227.

- [31] A. Akturk et al., "Compact and distributed modeling of cryogenic bulk MOSFET operation," *IEEE Trans. Electron Devices*, vol. 57, no. 6, pp. 1334–1342, Jun. 2010, doi: 10.1109/TED.2010.2046458.

- [32] Z. Zhu et al., "Design applications of compact MOSFET model for extended temperature range (60–400 K)," Electron. Lett., vol. 47, no. 2, pp. 141–142, Jan. 2011, doi: 10.1049/el.2010.3468.

- [33] P. Martin, A. S. Royet, F. Guellec, and G. Ghibaudo, "MOSFET modeling for design of ultra-high performance infrared CMOS imagers working at cryogenic temperatures: Case of an analog/digital 0.18 µm CMOS process," Solid-State Electron., vol. 62, no. 1, pp. 115–122, 2011, doi: 10.1016/j.ssc.2011.01.004.

- [34] Z. Chen, H. Wong, Y. Han, S. Dong, and B. L. Yang, "Temperature dependences of threshold voltage and drain-induced barrier lowering in 60 nm gate length MOS transistors," *Microelectron. Rel.*, vol. 54, nos. 6–7, pp. 1109–1114, Jun/Jul. 2014, doi: 10.1016/jmicrorel.2013.12.005.

- [35] H. Zhao and X. Liu, "Modeling of a standard 0.35

µm CMOS technology operating from 77K to 300K," Cryogenics, vol. 59, pp. 49–59, Jan. 2014, doi: 10.1016/j.cryogenics.2013.10.003.

- [36] G. S. Fonseca, L. B. de Sá, and A. C. Mesquita, "Extraction of static parameters to extend the EKV model to cryogenic temperatures," in *Proc. SPIE Defense Security*, Baltimore, MD, USA, May 2016, Art. no. 98192B. doi: 10.1117/12.2219734.

- [37] A. Beckers et al., "Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing," in Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC), Leuven, Belgium, Sep. 2017, pp. 62–65, doi: 10.1109/ESSDERC.2017.8066592.

- [38] N. C. Dao et al., "An enhanced MOSFET threshold voltage model for the 6–300 K temperature range," *Microelectron. Rel.*, vol. 69, pp. 36–39, Feb. 2017, doi: 10.1016/j.microel.2016.12.007.

- [39] R. M. Incandela et al., "Nanometer CMOS characterization and compact modeling at deep-cryogenic temperatures," in Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC), Leuven, Belgium, Sep. 2017, pp. 58–61, doi: 10.1109/ESSDERC.2017.8066591.

- [40] L. Varizat, G. Sou, M. Mansour, D. Alison, and A. Rhouni, "A low temperature 0.35µm CMOS technology BSIM3.3 model for space instrumentation: Application to a voltage reference design," in Proc. IEEE Int. Workshop Metrol. AeroSpace (MetroAeroSpace), Padua, Italy, Jun. 2017, pp. 74–78, doi: 10.1109/MetroAeroSpace.2017.7995541.

- [41] A. Rhouni et al., "First-ever test and characterization of the AMS standard bulk 0.35 μm CMOS technology at sub-Kelvin temperatures," J. Phys. Corff. Series, vol. 834, no. 1, May 2017, Art. no. 012005, doi: 10.1088/1742-6596/834/1/012005.

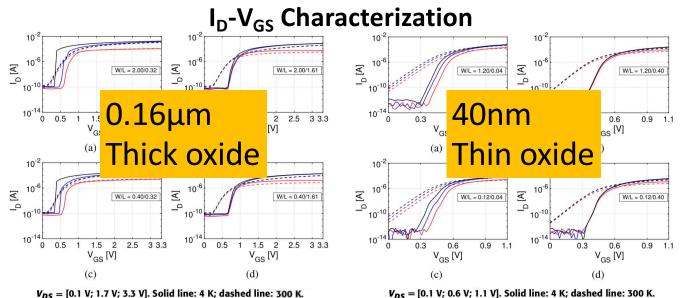

R.M. Incandela et al., J. of EDS 2018

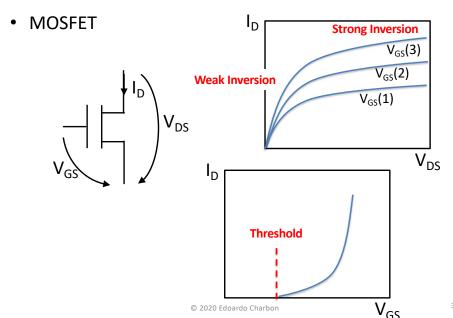

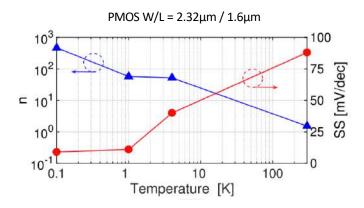

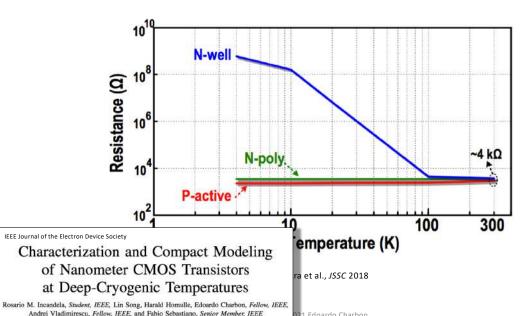

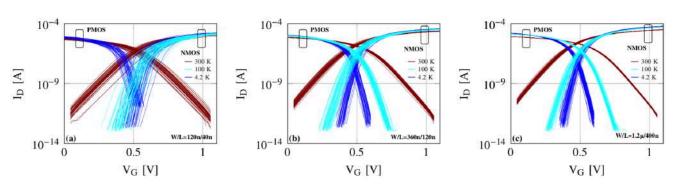

## What Happens to CMOS at Cryo?

- Threshold voltage increases significantly

- A current kink may appear

- Mismatch in passives and actives is more prominent

- The substrate becomes practically floating

- The SS is higher but it saturates around 1K

- Leakage drastically reduces

R.M. Incandela et al., ESSDERC 2017 R.M. Incandela et al., J. of EDS 2018

#### **How to Characterize MOS Transistors?**

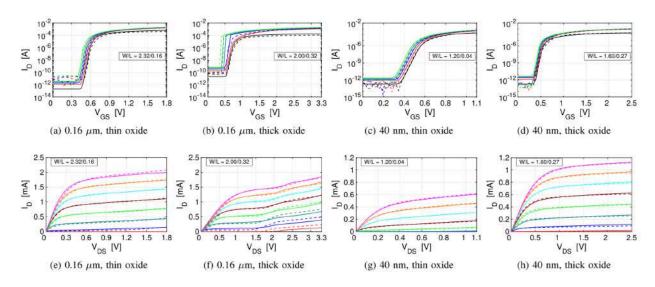

#### **CMOS Characterization in Practice**

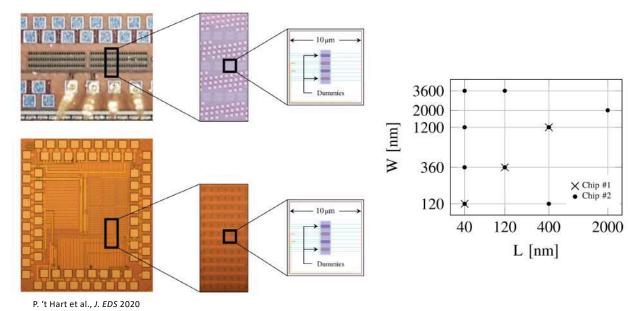

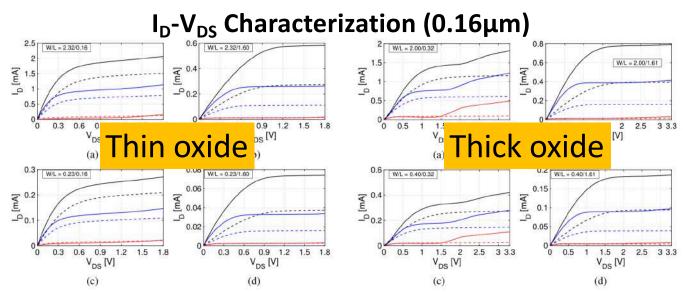

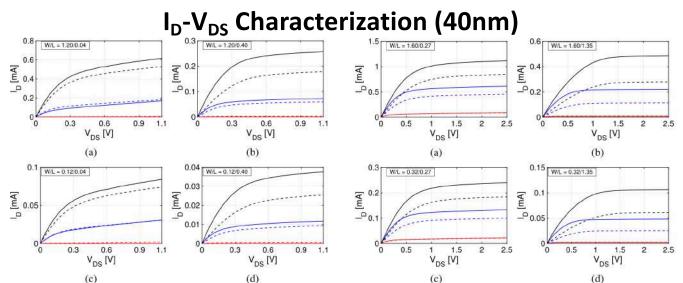

P. 't Hart et al., J. EDS 2020

R.M. Incandela et al., J. of EDS 2018

V<sub>GS</sub> = [0.68 V; 1.24 V; 1.8 V]. Solid line: 4 K; dashed line: 300 K.

V<sub>GS</sub> = [1.05 V; 2.17 V; 3.3 V]. Solid line: 4 K; dashed line: 300 K.

V<sub>GS</sub> = [0.43 V; 0.76 V; 1.1 V]. Solid line: 4 K; dashed line: 300 K.

V<sub>GS</sub> = [0.85 V; 1.68 V; 2.5 V]. Solid line: 4 K; dashed line: 300 K.

R.M. Incandela et al., J. of EDS 2018

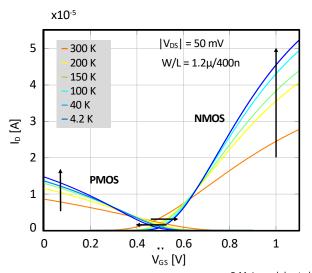

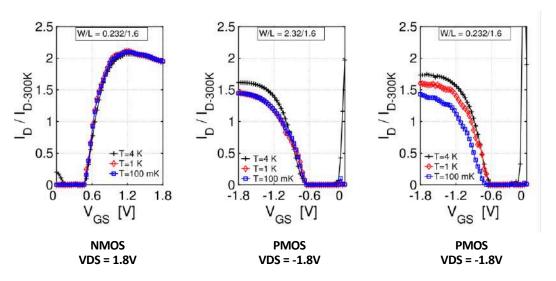

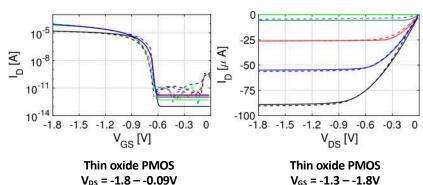

## **I**<sub>D</sub>-V<sub>GS</sub> Characterization in Sub-K Regimes

R.M. Incandela et al., J. of EDS 2018

## **CMOS Modeling**

|         | MOS11 pa | arameters for | 0.16-μm CM | OS   |     |

|---------|----------|---------------|------------|------|-----|

| BETSQR  | VFBR     | THESRR        | SDIBLO     | ALPR | KOR |

| THESATR | THERR    | A1R           | A2R        | A3R  |     |

|         | PSP pa   | rameters for  | 40-nm CMOS |      |     |

| FACTUO  | DELVTO   | THEMUO        | THESATO    | RSW1 | CFL |

| ALPL    | MUEO     | FBET1         |            |      |     |

•

## **CMOS Modeling**

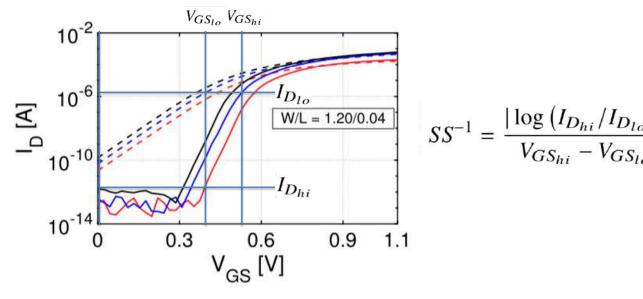

## **Sub-threshold Slope (SS)**

$$SS = \ln(10) \frac{kT}{q} \left( 1 + \frac{C_d}{C_{ox}} \right)$$

$C_d$  = depletion layer capacitance  $C_{ox}$  = gate oxide capacitance

$$SS = \ln(10) \frac{kT}{q} \sim 60 \text{mV/dec}$$

$$C_d = 0$$

;  $C_{ox} \rightarrow$  : thermionic limit

## **Sub-threshold Slope Characterization(SS)**

## **Sub-threshold Slope (SS)**

R.M. Incandela et al., ESSDERC 2017 R.M. Incandela et al., J. of EDS 2018

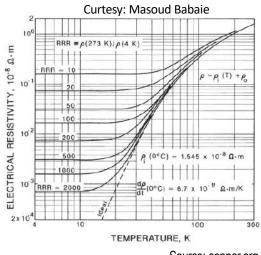

## **Substrate Resistivity**

# Mismatch Modeling at Cryo

## **Subthreshold Current Mismatch: Why Do We Care?**

- Impacts performance of:

- ADC/DAC

- Differential pairs

- SRAM

Worsens with technology scaling

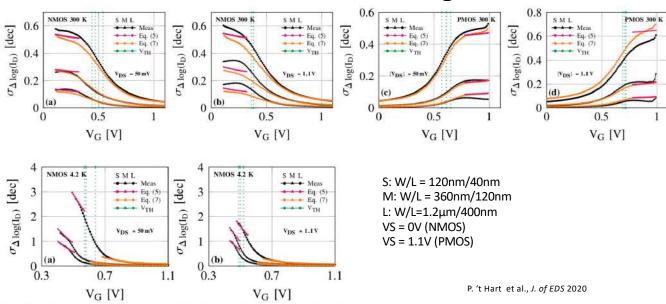

#### **Subthreshold Current Model**

$$I_D = I_0 e^{(V_{GS} - V_{TH})/SS}$$

Taylor expansion is impractical at cryo due to the instability of ID and the exponential nature of it.

Solve wrt  $log(I_D)$

$$\log{(I_D)} \propto \frac{1}{\ln(10)} \frac{V_{GS} - V_{TH}}{SS}.$$

Taylor expansion on  $V_{TH}$  and SS

$$\Delta \log (I_D) = \frac{1}{\ln(10)} \left( -\frac{1}{SS} \Delta V_{TH} - \frac{(V_{GS} - V_{TH})}{SS} \frac{\Delta SS}{SS} \right)$$

#### **Subthreshold Current Model**

$$\sigma_{\Delta \log I_D}^2 = \frac{1}{\ln(10)^2} \left[ \left( \frac{\sigma_{\Delta V_{TH}}}{\overline{SS}} \right)^2 + \left( \frac{V_{GS} - V_{TH}}{\overline{SS}} \frac{\sigma_{\Delta SS}}{\overline{SS}} \right)^2 + 2 \frac{(V_{GS} - V_{TH})}{\overline{SS}^3} \sigma_{\Delta V_{TH}} \sigma_{\Delta SS} \rho_{\Delta V_{TH}, \Delta SS} \right].$$

(5)

The correlation factor  $\rho$  between  $V_{\rm TH}$  and SS is generally negligible at 300K, 100K, and also at cryogenic temperatures.

#### **Croon Model**

$$\sigma_{\Delta I_D/I_D}^2 = \ln(10)^2 \sigma_{\Delta \log I_D}^2$$

$$\sigma_{\Delta \log I_D}^2 = \frac{1}{\ln(10)^2} \left[ \sigma_{\Delta\beta/\beta}^2 + \left( \frac{\bar{g}_m}{\bar{I}_D} \right)^2 \sigma_{\Delta V_{TH}}^2 \right], \tag{7}$$

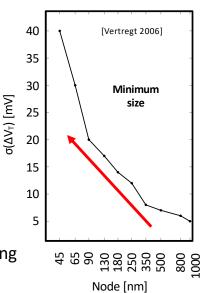

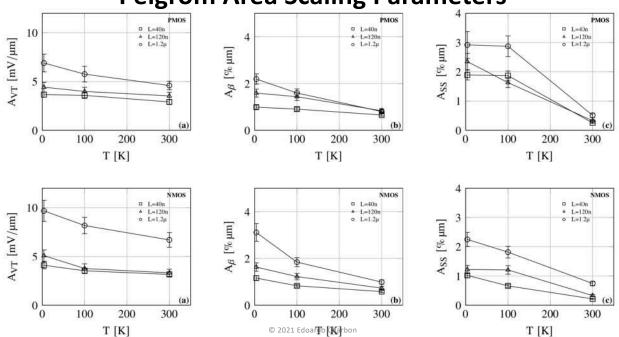

## **Pelgrom Scaling Law**

$$\sigma_{\Delta V_{TH}} = \frac{A_{VT}}{\sqrt{WL}}$$

$\sigma_{\Delta\beta/\beta} = \frac{A_{\beta}}{\sqrt{WL}}$   $\sigma_{\Delta SS/SS} = \frac{A_{SS}}{\sqrt{WL}}$

$A_{VT}$ : area scaling parameter for  $V_{\rm T}$   $A_{\beta}$ : area scaling parameter for  $\beta$   $A_{SS}$ : area scaling parameter for SS

W, L: transistor geometry parameters

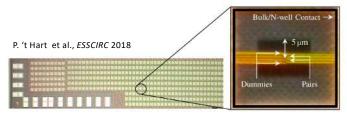

#### **How to Characterize Mismatch?**

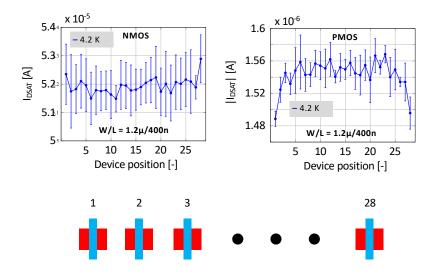

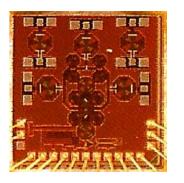

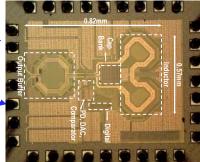

Fig. 1. Die micrograph (*left*) with close-up of a  $W/L = 1.2\,\mu\text{m}/0.4\,\mu\text{m}$  matched pair (*right*).

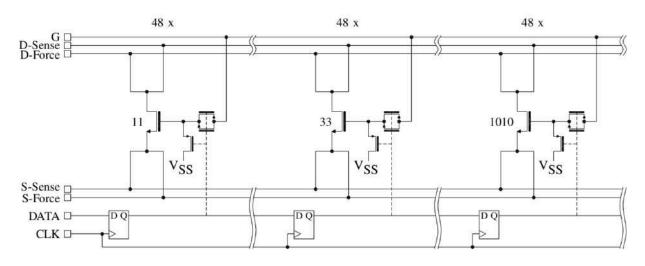

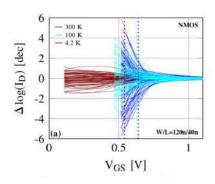

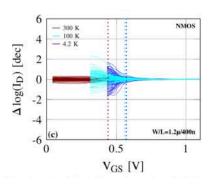

#### **Mismatch Measurements**

48 devices tested

$|V_{\rm DS}|$  = 50mV,  $V_{\rm S}$ =0V (NMOS)

$|V_{\rm DS}|$  = 50mV,  $V_{\rm S}$ =1.1V (PMOS)

P. 't Hart et al., J. of EDS 2020

## **Mismatch Measurements (2)**

6 - 300 K NMOS NMOS - 42 K NMO

72 device pairs tested  $V_{TH}$  in dashed lines  $|V_{\rm DS}|$  = 50mV

P. 't Hart et al., J. of EDS 2020

**Pelgrom Area Scaling Parameters**

## **Mismatch Modeling**

## **Position Dependence**

## **Summary on Threshold Mismatch**

Cryo-CMOS: mismatch follows Pelgrom and Croon models

Fixed V<sub>GS</sub> biasing → matching deteriorates up to 10x

• Fixed  $G_m/I_D$  biasing  $\rightarrow$  matching deteriorates "only" 1.1x

# Digital Modeling at Cryo

## **Lowerbound in Digital Design**

$$V_{DD,min} \approx 2 \frac{kT}{q} \ln(2) = 36 \text{mV}$$

CMOS circuits operate in subthreshold wherever this equation holds

$$I_{DS} = I_0 \frac{W}{L} e^{\frac{V_{GS} - V_{TH}}{nv_t}} \left( 1 - e^{\frac{-V_{DS}}{v_t}} \right); \ I_0 = \mu_0 C_{ox} \frac{W}{L} (n-1) v_t^2,$$

*n* is the sub-threshold slope (SS) factor and  $v_t = kT/q$ ,

The net effect in sub-threshold regimes is a decrease of leakage currents by orders of magnitude, implying a significant increase in the  $I_{ON}/I_{OFF}$  ratio

### **Lowerbound in Digital Design**

Assuming an ideal SS factor n = 1, at 4.2 K, according to well established room temperature models, one could theoretically achieve  $V_{DD,min} \approx 2 \ln(2) v_t = 0.48 \text{mV}$ .

However, at 4.2 K the consensus is that  $n\approx34.9$ . Thus, this fundamental limit is actually VDD, $min\approx2.47$ mV. Additional non-idealities include reverse short-channel effect (RSCE) and inverse narrow-width effect (INWE).

Both effects substantially modulate the threshold voltage.

## Latchup

Latch-up has been found to be unpredictable in deep-cryogenic operation. Latch-up immunity typically improves at temperatures lower than RT, thanks to lower well and substrate resistance and to higher base-emitter voltages and lower current gain of parasitic bipolar transistors. However, shallow level impact ionization (SLII), a mechanism for carrier generation, emerges below 50 K

#### Recommendations

- A)create extensive substrate contacts and well-taps, so as to minimize the chance of latch-up at 4.2 K;

- B) resize the transistors, so as to reduce INWE and thus maximize  $V_{TH}$  modulation;

- C) add secondary power rails to enable forward back-biasing, so as to compensate for an increase of  $V_{TH}$  at 4.2, in addition use low- $V_{TH}$  transistors;

- D)minimize the length of transistors (in contrast to conventional RT subthreshold standard cell design, where the opposite is generally done);

- E) when useful, make the layout aware of mismatch by increasing the overall height of the cells.

## Summary of Issues 300K -> 0.1K

- Threshold voltage increases significantly

- A current kink may appear

- Mismatch in passives and actives is more prominent

- The substrate becomes practically floating

- The SS is higher but it saturates around 1K

- Leakage drastically reduces

#### **Trends and Predictions**

- How will devices perform in 5 years at 77K?

- How will FinFETs/nanowire FET behave at 77K (Lg<20nm)</li>

- Will ballistic transport affect these devices?

- How different will optimization be at 77K?

- Is there a way to decrease V<sub>T</sub>?

## High-Level Modeling at Cryo

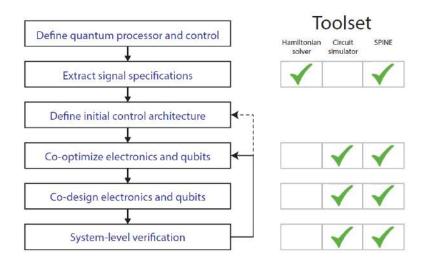

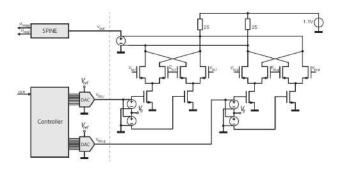

### **High-Level Modeling: SPINE (SPIN Emulator)**

#### **Objectives:**

- Enable co-design qubit/electronics

- Derive specifications for Horse Ridge and other components

- Minimize power to achieve wanted fidelity

#### Circuit simulator

# Qubit simulator (Hamiltonian)

#### **SPINE**

J. Van Dijk et al., DATE 2018

#### **SPINE**

• Microwave Carrier: **Keysight E8267D**

22.4 kHz resolution 1 mHz

-  $\mathcal{L}$  (1 MHz) = -106 dBc/Hz >15 dB better

$-S_n = 7.12 \text{ nV/VHz}$  63 nV/VHz

$\rightarrow$  > 20 dB attenuation

Microwave Envelope: Tektronix 5014C

8-bit resolution

14-bit

140 MS/s

3.56 ns<sub>rms</sub>

40 dB SNR

14-bit

1.2 GS/s

5.0 ps<sub>rms</sub>

better

With SPINE we checked that these specs are enough

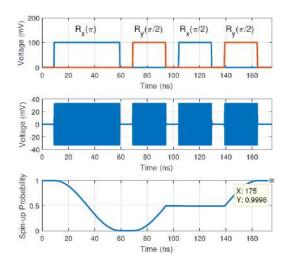

#### **SPINE**

- Example of full simulation:

- Sequence of rotations

- Resulting RF signals

- Qubit response, in terms of spin-up probability

- This involves spin emulation, M/S simulation, RF simulation

J. Van Dijk et al., DATE 2018

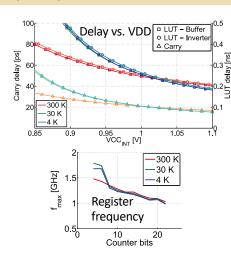

Cryogenic Reconfigurable Hardware

## **Cryo-FPGAs**

### **Cryo-FPGAs**

# CryoCMOS Hardware Technology A Classical Infrastructure for a Scalable Quantum Computer

**ACM Frontiers in Computing, Como 2016**

Harald Homulle<sup>1</sup>, Stefan Visser<sup>1</sup>, Bishnu Patra<sup>1</sup>, Giorgio Ferrari<sup>2</sup>, Enrico Prati<sup>3</sup>, Carmen G. Almudéver<sup>1</sup>, Koen Bertels<sup>1</sup>, Fabio Sebastiano<sup>1</sup>, Edoardo Charbon<sup>1</sup>

<sup>1</sup>QuTech, Delft University of Technology, Delft, The Netherlands

<sup>2</sup>Politecnico di Milano, Milano, Italy, <sup>3</sup>Consiglio Nazionale delle Ricerche, Milano, Italy {h.a.r.homulle, f.sebastiano, e.charbon}@tudelft.nl

### **FPGA** functionality

- All FPGA components are working in the cryogenic environment down to 4K

- · No modifications required

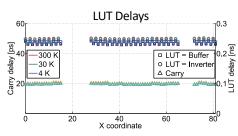

| Component | Functional   | Behavior                          |

|-----------|--------------|-----------------------------------|

| IOs       | ✓            |                                   |

| LVDS      | $\checkmark$ |                                   |

| LUTs      | ✓            | Delay change < 5%                 |

| CARRY4    | $\checkmark$ | Delay change < 2%                 |

| BRAM      | ✓            | No corruption (800 kB)            |

| MMCM      | $\checkmark$ | Jitter reduction of roughly 20%   |

| PLL       | ✓            | Jitter reduction of roughly 20%   |

| IDELAYE2  | $\checkmark$ | Delay change of up to 30%         |

| DSP48E1   | ✓            | No corruption over 400 operations |

#### **FPGA Performance**

Specs:

Carry: 20 vs. 8.4 ps at 300 K LUTs: 238 vs 235 ps at 300 K

Speed-up 2.4 vs 10.8% toward 300 K

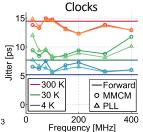

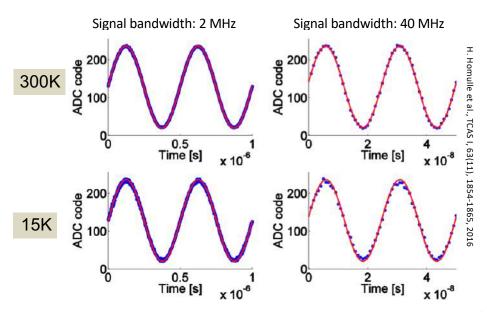

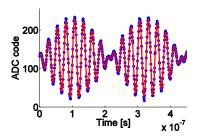

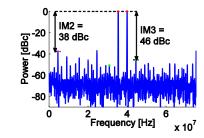

### ADC on FPGA (1.2GSa/s)

#### ADC on FPGA

- Two tones: ≈ 36 / 41 MHz

- IM2 = 38 dB

- IM3 = 46 dB

- Many secondary harmonics

- Interference with 100 MHz (sampling tone)

H. Homulle et al., TCAS I, 63(11), 1854-1865, 2016

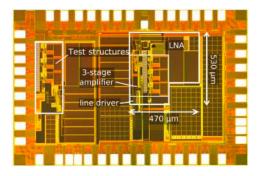

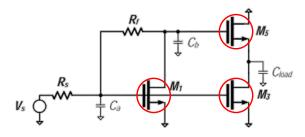

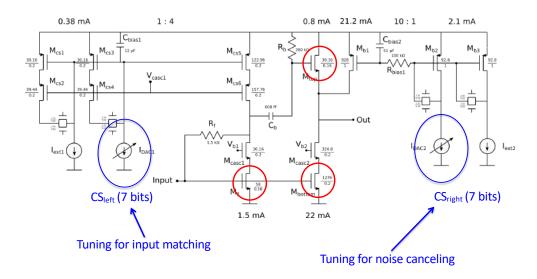

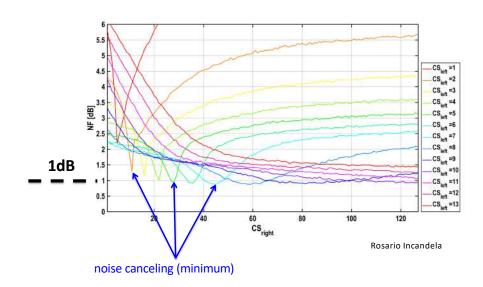

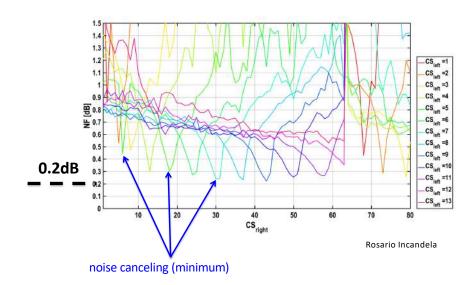

### **Low Noise Amplifiers (Cryo-LNAs)**

### **Cryo-LNA**

F. Bruccoleri et al., JSSC 2004

- Standard 160nm CMOS

- 500 MHz Bandwidth

- 0.1dB Noise figure

- 7K noise-equivalent temperature

### **Cryo-LNA**

### **Noise Figure at RT**

### Noise Figure at 4K

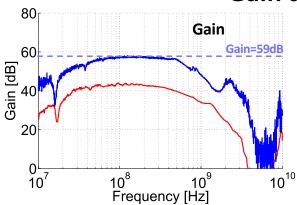

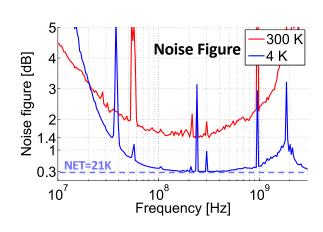

### **Gain and Noise**

B. Patra, R. Incandela et al, JSSC 2018

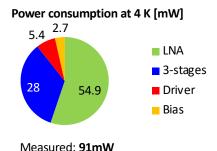

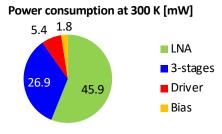

#### **Power**

Measured: 80mW

Sharing 150x 1MHz-channels (one channel per qubit)

0.61mW per qubit

Rosario Incandela

### Can We Do Better?

| Amplifier<br>Metrics         | Cryogenic<br>HEMT | JPA                            | TWPA 1.0                  | TWPA 2.0                  |  |

|------------------------------|-------------------|--------------------------------|---------------------------|---------------------------|--|

| Power<br>Dissipation         | 16 mW             | 100 pW                         | 1 nW                      | 5 nW                      |  |

| Bandwidth<br>(>15 dB gain)   | 11 GHz            | 100 - 200 MHz                  | 6 GHz                     | 5 GHz                     |  |

| 1-dB<br>Compression<br>point | 0 dBm             | -110 dBm<br>(3 qubits)         | -95 dBm<br>(20-30 qubits) | -85 dBm<br>(> 100 qubits) |  |

| Noise<br>Temperature         | 5 K               | 400 mK                         | 400 mK                    | 400 mK                    |  |

| External<br>Hardware         | Isolator          | Direct. Coupler,<br>Circulator | Direct. Coupler           | None                      |  |

#### Can We Do Better?

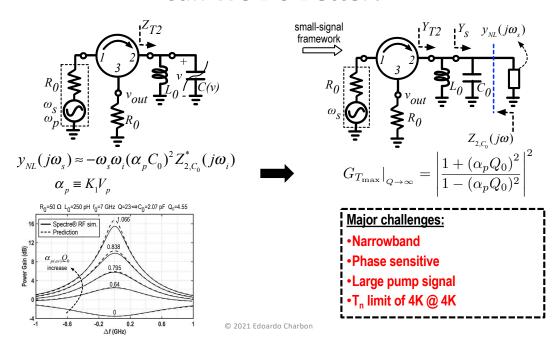

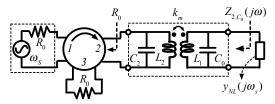

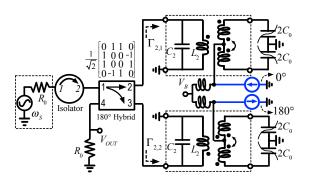

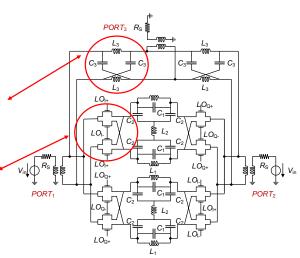

### **CMOS Parametric Amplifier**

#### 1) Transformer-based parametric amplifier

✓ Allow for broadband operation

#### 2) CM impedance peaking

- ✓ Suppress the pump signal leak

- ✓ Reduce pump power consumption

#### 3) "image"-rejection architecture

- ✓ Double the usable RF bandwidth.

- ✓ Phase-insensitive operation

- ✓ Allow for T<sub>n</sub> limit of below 4K

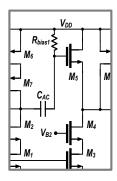

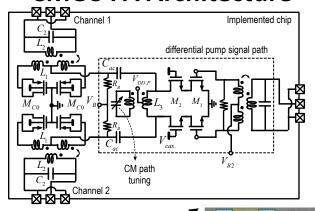

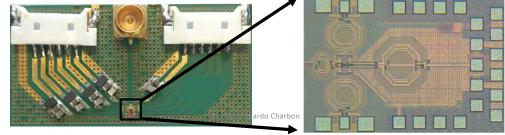

### **CMOS PA Architecture**

M. Mehrpoo, F. Sebastiano, E. Charbon, M. Babaie, *Solid-State Circuit Letters*, 2020

$0.825 \ mm^2$

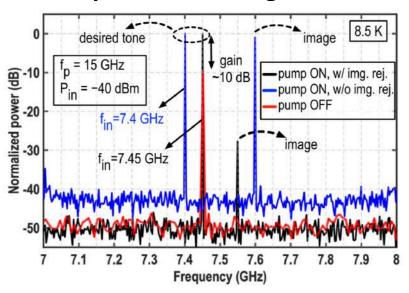

### **Spectrum of Single Tone**

M. Mehrpoo, F. Sebastiano, E. Charbon, M. Babaie, Solid-State Circuit Letters, 2020

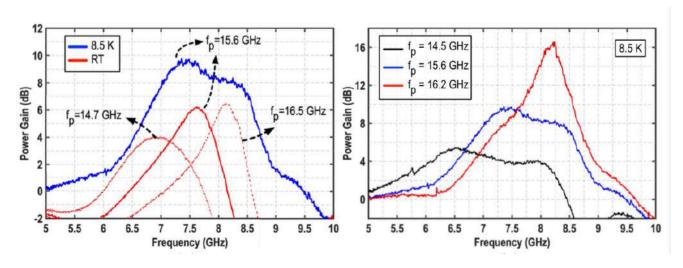

### Power Gain vs. Pump Frequency and Temperature

M. Mehrpoo, F. Sebastiano, E. Charbon, M. Babaie, Solid-State Circuit Letters, 2020

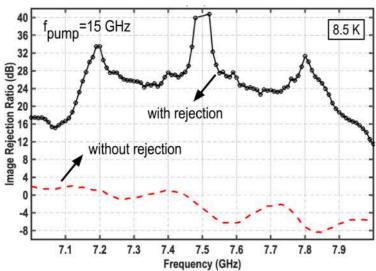

### **Image Rejection**

M. Mehrpoo, F. Sebastiano, E. Charbon, M. Babaie, Solid-State Circuit Letters, 2020

### **CMOS Passive Circulators & Multiplexers**

#### **Transmission Line Circulator**

S-parameters at  $\omega_{in}$ =  $3\omega_m$

$$S = \begin{bmatrix} 0 & 0 & -1 \\ -j & 0 & 0 \\ 0 & -j & 0 \end{bmatrix}$$

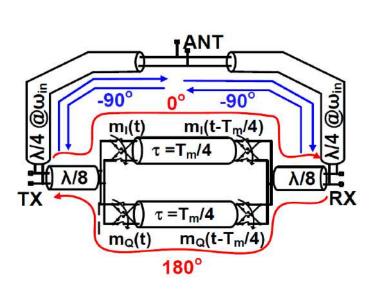

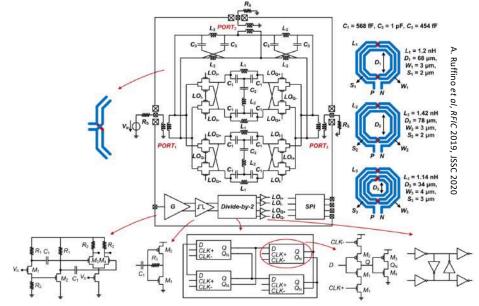

### **Passive Circulator Architecture**

Non-reciprocal behavior due to staggered commutation

Passive LC all-pass filters

Passive mixers with nonoverlapping I/Q phases

On-chip LO divider and I/Q generation

SPI control for tunability

$P_{DC} = 1.7 \text{ mW}$  $P_{AUX} = 8 \text{ mW}$

### **Passive Circulator Architecture**

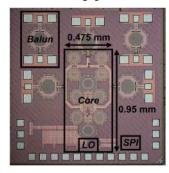

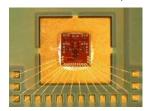

### **CMOS 40 nm Circulator Prototype**

- TSMC CMOS 40 nm technology

- Tape-out, PCB design and measurements at 300 K and 4.2 K

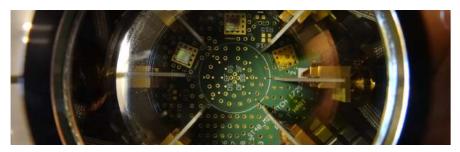

- RF probing with LakeShore CPX probe station

A. Ruffino et al, RFIC 2019, JSSC 2020

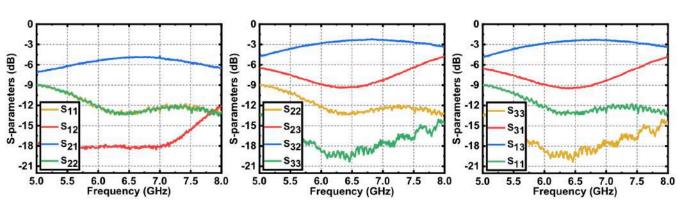

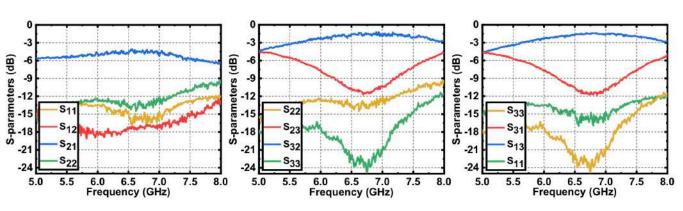

### **Measured S-parameters (300K)**

A. Ruffino et al, RFIC 2019, JSSC 2020

### **Measured S-parameters (4.2K)**

A. Ruffino et al, RFIC 2019, JSSC 2020

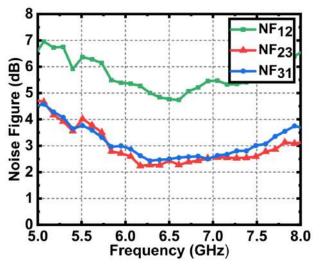

### **Circulator Noise Figure (300K)**

Minimum noise figure of 2.1 dB is measured, consistent with insertion loss measurements. There is no excess noise from clock generation path.

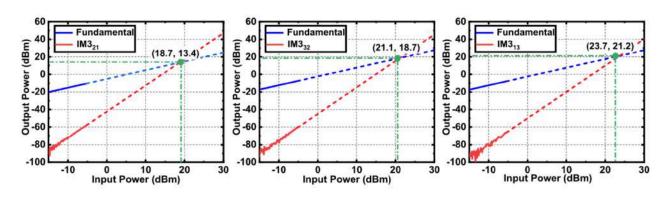

### **Circulator Linearity (300K)**

A. Ruffino et al, RFIC 2019, JSSC 2020

High linearity is measured in all directions, due to the quasi-passive nature of the circulator.

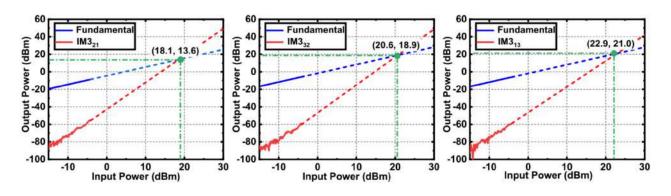

### **Circulator Linearity (4.2K)**

A. Ruffino et al, RFIC 2019, JSSC 2020

High linearity is measured in all directions, due to the quasi-passive nature of the circulator.

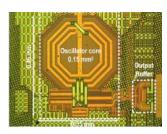

## **Cryo-Oscillators**

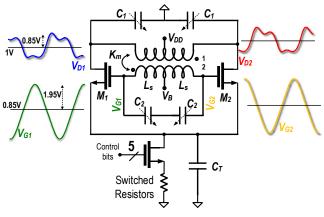

## **Cryo-Oscillator (Class F)**

M. Shahmohammadi, ISSCC 2015

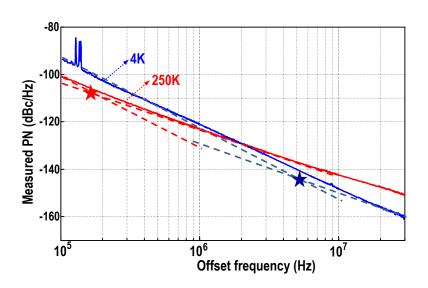

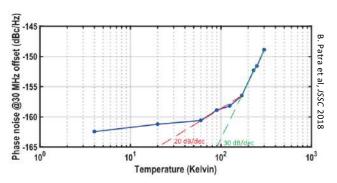

#### **Phase Noise**

#### **Measured Phase Noise**

#### Sources of noise:

- Thermal noise

- Shot noise

- Impurities in copper

Source: copper.org

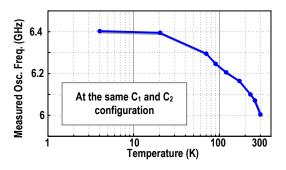

## **Frequency Stability**

B. Patra et al, JSSC 2018

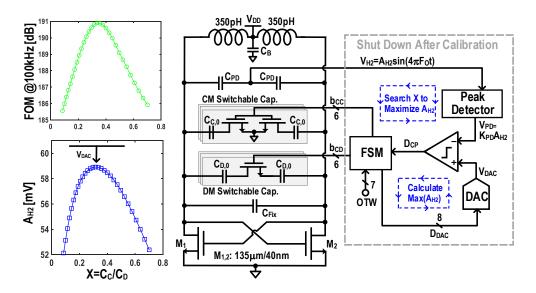

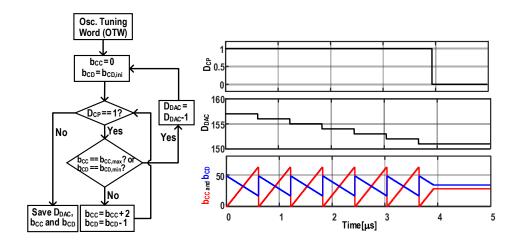

#### **Improving Frequency Stability**

## **Improving Frequency Stability (2)**

J. Gong, F. Sebastiano, E. Charbon, M. Babaie, ISSCC 2020

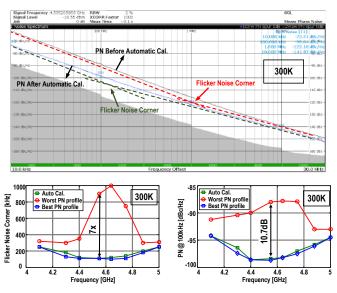

#### Phase Noise at 300K

J. Gong, F. Sebastiano, E. Charbon, M. Babaie, ISSCC 2020

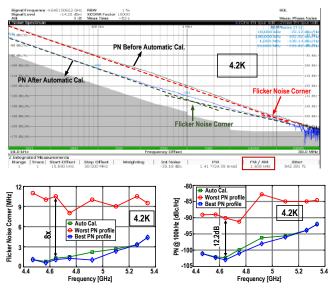

#### Phase Noise at 4K

J. Gong, F. Sebastiano, E. Charbon, M. Babaie, ISSCC 2020

### Implementation in 40nm CMOS Node

#### Measurements at RT:

Technology: 40nm CMOS

F<sub>out</sub>: 4.05-5.16GHz (24.1%)

F<sub>ref</sub>: 20MHz

Supply: 0.5V (oscillator core) Power consumption: 3.2mW

PN @10MHz: -141.5dBc/Hz

PN@100kHz:-98.8dBc/Hz

## **Cryo-Logic**

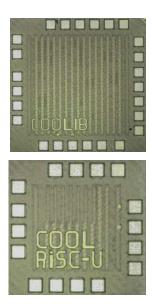

#### **Ultra-Low Voltage Library 'cooLib'**

- Digital library optimized for 4K

- Ultra low voltage operation (100s mV)

- Sub-threshold bias of N/P MOS

- · Resilient to latchup and hysteresis-free

- Several logic families (static and dynamic CMOS)

- Compatible with commercial P&R tools

D-Flip-flop optimized for 4K (40nm CMOS)

12

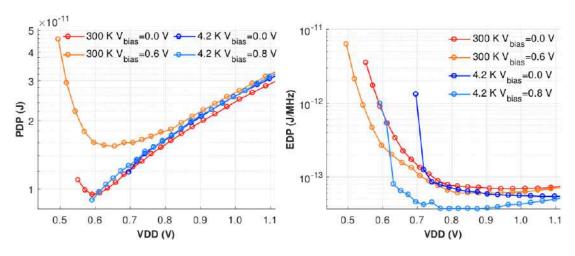

#### **Test Chip Implementation**

- Compare 'CooLib' cells to foundry supplied std. cells of TSMC40LP process

- Contains commonly encountered digital circuits

- i.e. unsigned multiplier

- Four versions per circuit

- Static 'CooLib'

- Domino 'CooLib'

- TSMC40LP, restricted

- TSMC40LP, unrestricted

- One 'true' domino logic implementation

E. Schriek et al., IEEE Solid-State Circuits Letters 2020

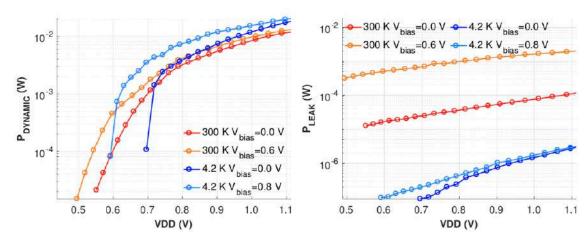

#### **Dynamic vs. Static Power at Cryo**

#### **FOMs**

PDP: power-delay product EDP: energy-delay product

## **Benchmarking**

| Benchmark                    | Temp. | $V_{DD,MIN}$ [V] |      | $F_{MAX} @ 0.6 \text{ V [MHz]}$ |               |      | $F_{MAX} @ 0.7 \text{ V [MHz]}$ |               |       | $P_{AVG}$ @ 100 kHz $[\mu W]$ |               |       |       |

|------------------------------|-------|------------------|------|---------------------------------|---------------|------|---------------------------------|---------------|-------|-------------------------------|---------------|-------|-------|

|                              |       | Pro-<br>posed    | A    | В                               | Pro-<br>posed | A    | В                               | Pro-<br>posed | A     | В                             | Pro-<br>posed | A     | В     |

| 16X16<br>Multiplier          | 4.2 K | 0.54             | 0.68 | 0.68                            | 16.3          | (5)  | S#3                             | 74.2          | 4.6   | 2.0                           | 2.34          | 3.76  | 3.88  |

|                              | 300 K | 0.3              | 0.49 | 0.44                            | 100.4         | 9.7  | 17.4                            | 145.2         | 34.0  | 39.7                          | 0.61          | 2.68  | 1.92  |

| EPFL<br>Sine                 | 4.2 K | 0.58             | 0.68 | 0.68                            | 1.95          | -    |                                 | 20.9          | 2.2   | 1.1                           | 3.91          | 4.00  | 4.46  |

|                              | 300 K | 0.39             | 0.34 | 0.39                            | 15.2          | 9.2  | 9.5                             | 29.6          | 25.5  | 26.4                          | 3.46          | 2.11  | 2.18  |

| EPFL Int-<br>to-Float        | 4.2 K | 0.54             | 0.68 | 0.68                            | 51.4          | (4)  | 1923                            | 178.1         | 42.5  | 11.7                          | 0.80          | 1.57  | 3.41  |

|                              | 300 K | 0.24             | 0.38 | 0.36                            | 118.5         | 75.2 | 73.44                           | 174.2         | 191.9 | 158.0                         | 0.08          | 0.55  | 0.28  |

| EPFL Round-<br>Robin Arbiter | 4.2 K | 0.58             | 0.68 | 0.68                            | 21.6          | (+)  | -                               | 46.6          | 2.0   | 1.8                           | 7.89          | 11.56 | 11.64 |

|                              | 300 K | 0.32             | 0.32 | 0.31                            | 33.7          | 10.0 | 34.7                            | 59.9          | 37.3  | 80.8                          | 1.72          | 3.20  | 2.25  |

E. Schriek et al., IEEE Solid-State Circuits Letters 2020

#### 'CooLib' RISC-V Implementation

#### **FEATURES**

RISC-V (picorv32, open-source) implemented using 'CooLib'

## Fully functional μP operating at 4K

E. Schriek et al., IEEE Solid-State Circuits Letters 2020

- Interfacing by 'CooLib' level-shifters

- UART interface for serial in/output

- JTAG interface for SRAM write/read

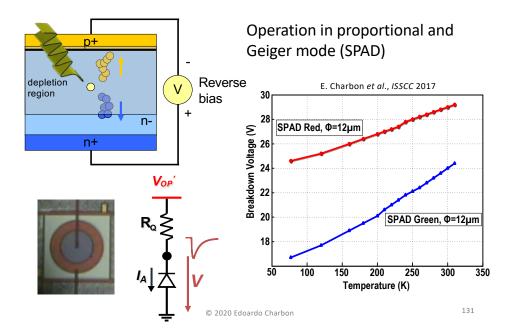

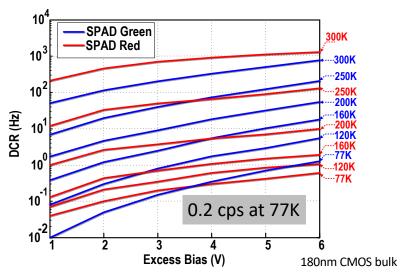

#### **Cryo-Single-Photon APDs (Cryo-SPADs)**

### **Cryo-SPADs**

B. Patra et al., JSSC 2018

# Qubits and Control in the Fridge

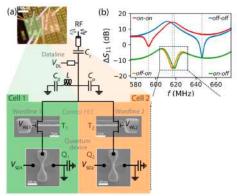

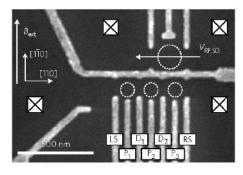

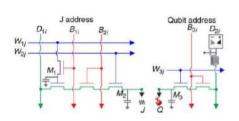

#### **Step 1: Multiplexing Qubits**

## **Step 2: Reading Qubits**

- Single-shot dispersive readout

- Single electron transistor readout

- · (limited) use of 3D stacking

- Ideally bring qubits to 1-4K, make them CMOS-compatible

H. Homulle et al., QuRO interface Silicon Quantum Electronics Workshop, 2018

#### **Step 3: Controlling Qubits**

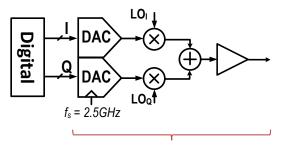

#### ➤ Lower Speed DAC + Mixer

**Analog**: noise/linearity specifications known + feasible

#### **Controlling Qubits: Specs**

• Target fidelity: 99.99% for 1...10 MHz operation

#### Analog:

| Error Source              | Туре       | Value                   | Contribution   |  |

|---------------------------|------------|-------------------------|----------------|--|

| Microwave frequency       | inaccuracy | 35.4 kHz                | 1-F = 12.5 ppm |  |

| (nominally 513 GHz)       | noise      | 35.4 kHz <sub>rms</sub> | 1-F = 12.5 ppm |  |

| Microwave phase           | Inaccuracy | 0.20 °                  | 1-F = 12.5 ppm |  |

|                           | noise      | 0.20 °                  | 1-F = 12.5 ppm |  |

| Microwave amplitude       | inaccuracy | 38.3 μV                 | 1-F = 12.5 ppm |  |

| (nominally 17 mV, -53 dB) | noise      | 38.3 μVrms              | 1-F = 12.5 ppm |  |

| Microwave duration        | inaccuracy | 113 ps                  | 1-F = 12.5 ppm |  |

| (nominally 50 ns)         | noise      | 113 psrms               | 1-F = 12.5 ppm |  |

F = 99.99%

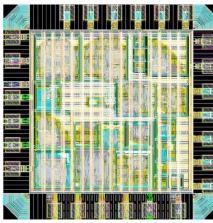

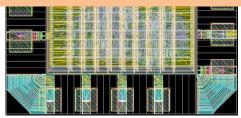

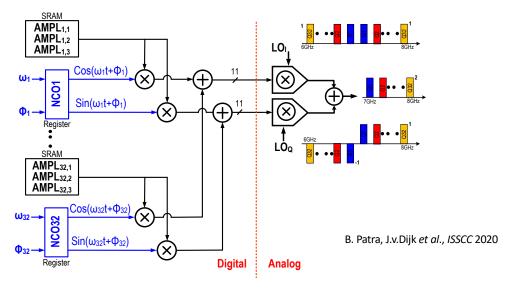

#### **Controller Architecture: Horse Ridge**

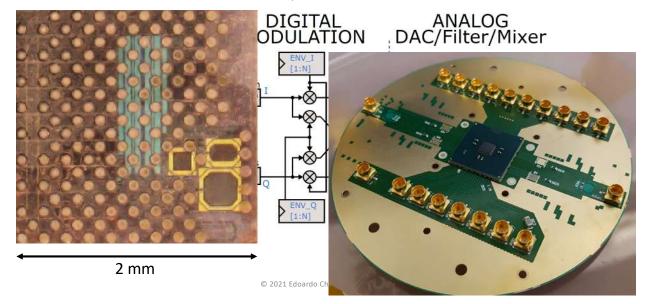

### **Controller Implementation**

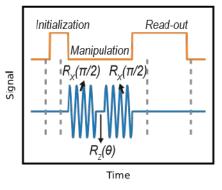

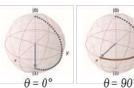

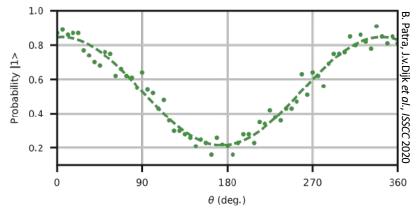

B. Patra, J.v.Dijk et al., ISSCC 2020

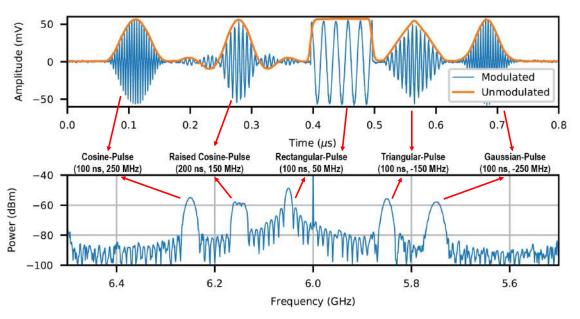

## **Pulse Shaping**

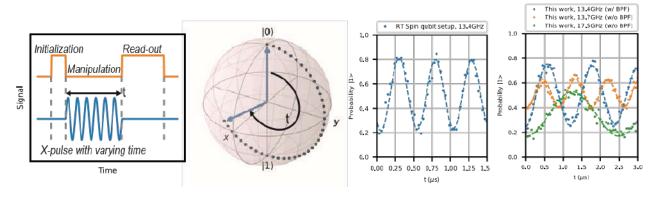

## Rabi Experiment

B. Patra, J.v.Dijk et al., ISSCC 2020

## **Qubit Manipulation**

## **Comparison Table**

|                                | Horse Ridge (ISSCC'20)                      | ISSCC'19                              | RSI'17     | Spin qubit setup |

|--------------------------------|---------------------------------------------|---------------------------------------|------------|------------------|

| Operating Temperature          | 3 K                                         | 3 K                                   | 300 K      | 300 K            |

| Qubit platform                 | Spin qubits + Transmons                     | Transmons                             | Transmons  | Spin qubits      |

| Qubit frequency                | 2 – 20 GHz                                  | 4 – 8 GHz                             |            | < 20 GHz         |

| Channels                       | 128 (32 per TX)                             | 1                                     | 4          | 1                |

| FDMA                           | Yes, SSB                                    | No                                    | Yes, SSB   | No               |

| Data Bandwidth                 | 1 GHz                                       | 400 MHz                               | 960 MHz    | 520 MHz          |

| Image & LO leakage calibration | On chip                                     | Off chip                              | Yes        |                  |

| Phase correction               | Yes                                         | No                                    | No         | No               |

| Fidelity (expected)            | 99.99%                                      | -                                     | -          | -                |

| Waveform/Instructions          | Upto 40960 pts AWG                          | Fixed 22 pts symmetric                |            | 16M pts AWG      |

| Instruction set                | Yes                                         | No                                    | Yes        | Yes              |

| Power / TX                     | Analog: 1.7 mW/qubit *<br>Digital: 330 mW ‡ | Analog < 2 mW/qubit #<br>Digital: N/A |            | 850 W            |

| Chip area / TX                 | 4 mm <sup>2</sup>                           | 1.6 mm <sup>2</sup>                   | Discrete   | Rack mount       |

| Technology                     | 22 nm FinFET CMOS                           | 28 nm bulk CMOS                       | components |                  |

<sup>\*</sup> including LO/Clock driver; only RF-Low active # does not mention circuits included

<sup>&</sup>lt;sup>‡</sup> can be reduced with clock gating

## 5. Conclusions

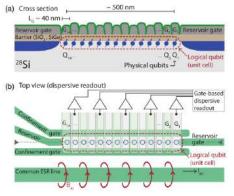

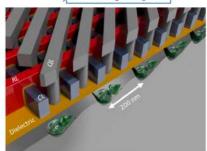

# Realizations of 1D Qubit Arrangements

Baart et al, Nat Nano (2017)

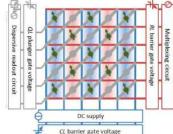

## **Proposals for Scalable Fault-Tolerant**

**2D Qubit Arrangements**

M. Veldhorst et al. (UNSW), Nature Comm. (2017)

R. Li et al., arXiv 1711.03807 (2017)

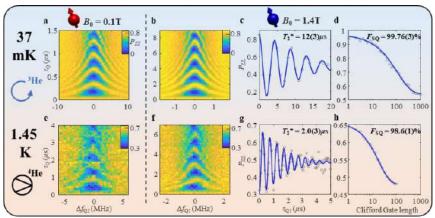

#### SiMOS QD Qubit Operation at 1.5 Kelvin

Silicon quantum processor unit cell operation above one Kelvin

C. H. Yang,<sup>1,\*</sup> R. C. C. Leon,<sup>1</sup> J. C. C. Hwang,<sup>1,†</sup> A. Saraiva,<sup>1</sup> T. Tanttu,<sup>1</sup> W. Huang,<sup>1</sup> J. Camirand Lemyre,<sup>2</sup> K. W. Chan,<sup>1,‡</sup> K. Y. Tan,<sup>1,‡</sup> F. E. Hudson,<sup>1</sup> K. M. Itoh,<sup>3</sup> A. Morello,<sup>1</sup> M. Pioro-Ladrière,<sup>2,4</sup> A. Laucht,<sup>1</sup> and A. S. Dzurak<sup>1,§</sup>

⇒ 1.5 K performance comparable to <sup>nat</sup>Si at 100 mK!

Courtesy: A. Dzurak

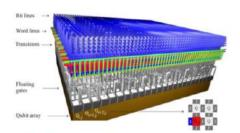

#### Platforms for the 2D Approach

- Single-shot dispersive readout could be the core of column readouts

- Use *imaging sensor* readout as inspiration

- Use tunneling barriers as selectors

- (limited) use of 3D stacking

- Ideally bring qubits to 1-4K, make them CMOS-compatible

#### **Tradeoffs**

#### 1-qubit gate:

Oscillator phase noise Timing accuracy

...

<u>2-qubit gate:</u> Voltage drift Timing jitter ...

Power

(~ 1 mW/qubit)

#### **Qubit read-out:**

Amplitude noise

...

- Fidelity is usually expressed as a percentage, ofter referred to as x9's (e.g. 5 9's = 99.999%)

- Higher fidelity usually requires high power, which is budgeted, espcially at low temperatures (e.g. μW of thermal absorption at mK, while W at 4K)

#### **Quantum Computing**

- A quantum computer is a new computing paradigm and as such it holds the promise to handle today's intractable problems

- A qubit is fragile and thus needs to be constantly corrected to extend its coherence and to maintain fidelity

- Cryogenic electronics for quantum computing ensures compactness and scalability to much larger quantum processors

## IceQubes: International Workshop on Cryogenic Electronics for Quantum Systems

June 2021, Neuchâtel - Switzerland